## Microprocessors and Microcontrollers

Architecture, Programming and Interfacing using 8085, 8086, 8051

## **ABOUT THE AUTHOR**

**Soumitra Kumar Mandal** holds a BE (Electrical Engineering) from Bengal Engineering College, Shibpur, Calcutta University, and an MTech (Electrical Engineering) with specialization in Power Electronics from the Institute of Technology, Banaras Hindu University, Varanasi. He obtained a PhD from Panjab University, Chandigarh. Prof. Mandal started his career as a lecturer of Electrical Engineering at SSGM College of Engineering, Shegaon. Thereafter, he joined as a lecturer at Panjab Engineering College, Chandigarh, and served there from March 1999 to January 2004. Then he joined National Institute of Technical Teachers' Training and Research, Kolkata, as Assistant Professor in Electrical Engineering in February 2004 and is presently working as Associate Professor.

Prof. Mandal is a life member of ISTE and a member of IE. Throughout his academic career, he has published about twenty-five research papers in national and international journals and presented many papers in national and international conferences. His research interests are in computer-controlled drives, microprocessor- and microcontroller-based system design, embedded system design and neuro-fuzzy computing.

The author can be contacted at his email id: mandal\_soumitra@yahoo.com.

## Microprocessors and Microcontrollers

Architecture, Programming and Interfacing using 8085, 8086, 8051

Soumitra Kumar Mandal

Associate Professor Department of Electrical Engineering National Institute of Technical Teachers' Training and Research Kolkata

Tata McGraw Hill Education Private Limited NEW DELHI

McGraw-Hill Offices

New Delhi New York St Louis San Francisco Auckland Bogotá Caracas Kuala Lumpur Lisbon London Madrid Mexico City Milan Montreal San Juan Santiago Singapore Sydney Tokyo Toronto

Published by Tata McGraw Hill Education Private Limited, 7 West Patel Nagar, New Delhi 110 008

#### **Microprocessors and Microcontrollers**

Copyright © 2011, Tata McGraw Hill Publishing Company Limited No part of this publication can be reproduced or distributed in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise or stored in a database or retrieval system without the prior written permission of the publishers. The program listings (if any) may be entered, stored and executed in a computer system, but they may not be reproduced for publication.

This edition can be exported from India only by the publishers, Tata McGraw Hill Education Private Limited

ISBN (13 digits) : 978-0-07-1329200 ISBN (10 digits) : 0-071-32920X

Vice President and Managing Director—McGraw-Hill Education–Asia Pacific Region: *Ajay Shukla* Head—Higher Education Publishing and Marketing: *Vibha Mahajan*

Publishing Manager—(SEM & Tech. Ed.): Shalini Jha Editorial Executive: Smruti Snigdha Editorial Researcher: Noaman Khan Executive—Editorial Services: Sohini Mukherjee Sr Production Manager: Satinder S Baveja Production Executive: Anuj K Shriwastava Marketing Manager—Higher Education: Vijay S Jagannathan

Senior Product Specialist (SEM & Tech Ed.): John Mathews

General Manager—Production: *Rajender P Ghansela* Assistant General Manager—Production: *B L Dogra*

Information contained in this work has been obtained by Tata McGraw-Hill, from sources believed to be reliable. However, neither Tata McGraw-Hill nor its authors guarantee the accuracy or completeness of any information published herein, and neither Tata McGraw-Hill nor its authors shall be responsible for any errors, omissions, or damages arising out of use of this information. This work is published with the understanding that Tata McGraw-Hill and its authors are supplying information but are not attempting to render engineering or other professional services. If such services are required, the assistance of an appropriate professional should be sought.

Typeset at Print-O-World, 2579, Mandir Lane, Shadipur, New Delhi 110 008, and printed at Adarsh Printers, C-50-51, Mohan Park, Naveen Shahdara, Delhi 110 032

Cover : A. P. OFFSET

RAXYYDAGDCQYA

The **McGraw Hill** Companies

## Dedication

To the memory of My youngest son, Late Gajanan Mandal And to My parents, Smt. Arati Mandal and Shri Prokash Mandal My wife, Malvika, and my children, Om and Puja

Soumitra Kumar Mandal

## CONTENTS

| Preface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | xiii |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <ul> <li>1. Introduction to Microprocessors and Microcontrollers <ol> <li>Introduction 1</li> <li>Microprocessor 3</li> <li>Microcomputer 4</li> <li>Architecture of Microprocessors 6</li> <li>History of Microprocessors 8</li> <li>Evolution of Microprocessors 9</li> <li>Microprocessor Applications 12</li> <li>Evolution of Microcontrollers 13</li> <li>Applications of Microcontrollers 15</li> <li>Summary 16</li> <li>Multiple-Choice Questions 16</li> <li>Short-Answer-Type Questions 17</li> <li>Review Questions 17</li> <li>Answers to Multiple-Choice Questions 17</li> </ol> </li> </ul> | 1    |

| <ul> <li>2. Architecture of the 8085 Microprocessor</li> <li>2.1 Introduction 18</li> <li>2.2 Block Diagram of the 8085 Microprocessor 18</li> <li>2.3 Pin Diagram of 8085 Microprocessor 28</li> <li>Summary 33</li> <li>Multiple-Choice Questions 34</li> <li>Short-Answer-Type Questions 35</li> <li>Review Questions 35</li> <li>Answers to Multiple-Choice Questions 36</li> </ul>                                                                                                                                                                                                                    | 18   |

| <ul> <li>3. Instruction Set and Addressing Modes of 8085 Microprocessor</li> <li>3.1 Introduction 37</li> <li>3.2 Addressing Modes 37</li> <li>3.3 Instruction Set 40</li> <li>3.4 Instruction and Data Formats 43</li> <li>3.4 Symbols and Abbreviations 45</li> <li>3.5 8085 Instructions 46</li> <li>3.6 Instruction Timing Diagram 63</li> <li>3.7 Timing Diagram 66</li> </ul>                                                                                                                                                                                                                        | 37   |

Summary 77 Multiple-Choice Questions 77 Short-Answer-Type Questions 79 Review Questions 79 Answers to Multiple-Choice Questions 80

#### 4. Assembly – Language Programs of the 8085 Microprocessor

- 4.1 Introduction 81

- 4.2 Machine Language 82

- 4.3 Assembly Language 82

- 4.4 High-Level Language 83

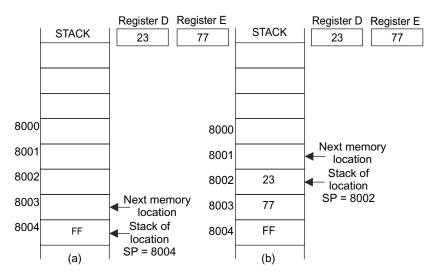

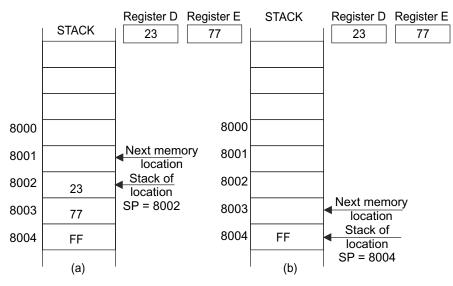

- 4.5 Stack 87

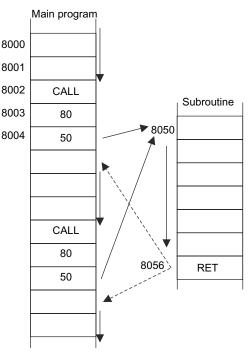

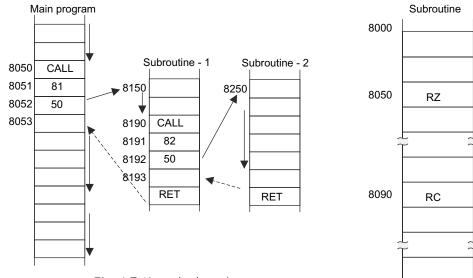

- 4.6 Subroutines 89

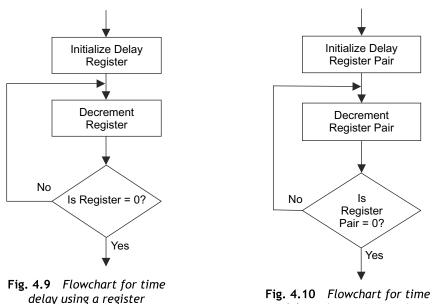

- 4.7 Time-Delay Loops 91

- 4.8 Modular Programming 94

- 4.9 Macro 95

4.10 Instruction Format 96

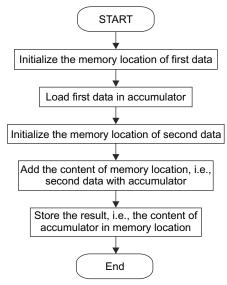

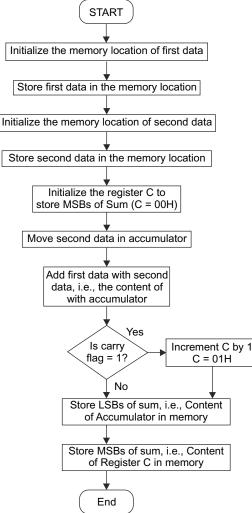

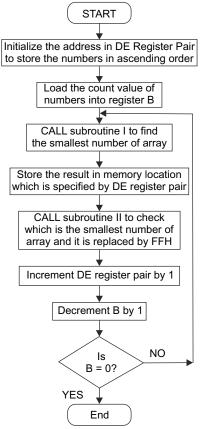

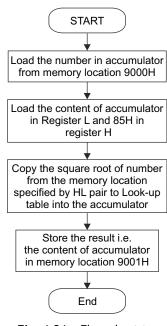

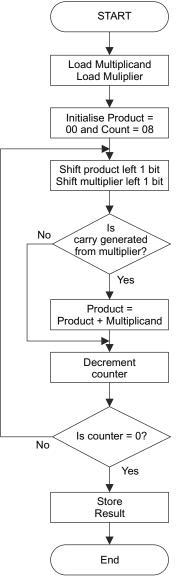

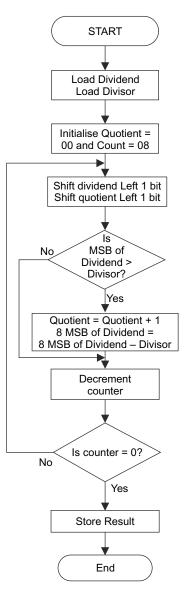

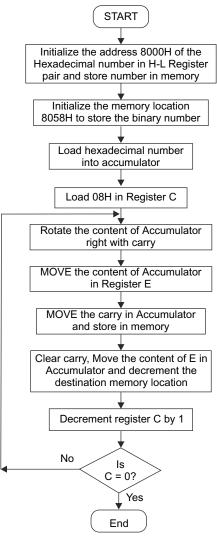

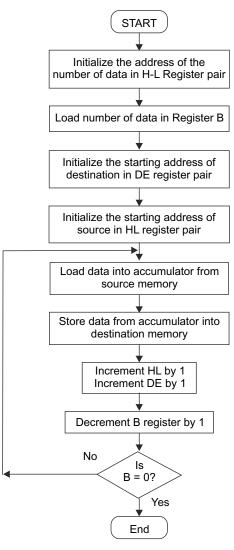

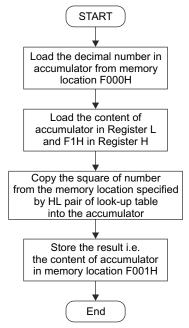

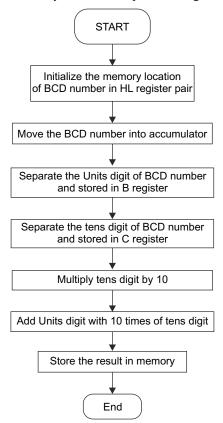

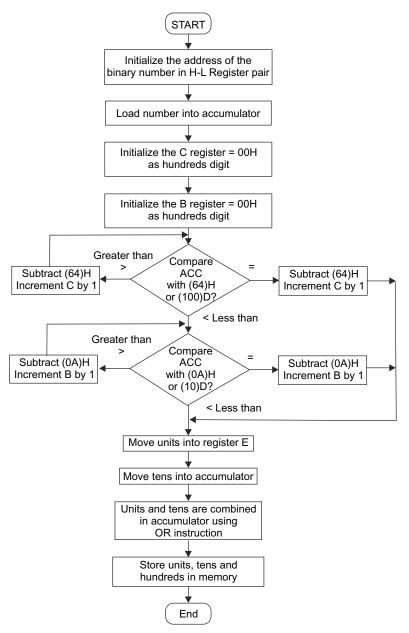

4.11 Assembly-Language Programs 97

Summary 142

Multiple-Choice Questions 142 Short-Answer-Type Questions 144 Review Questions 145 Answers to Multiple-Choice Questions 146

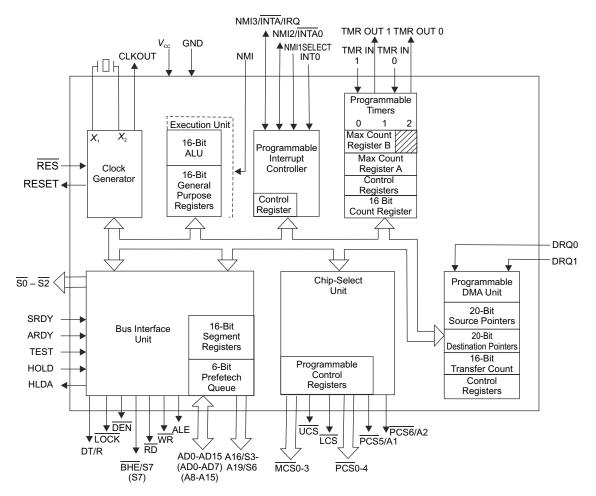

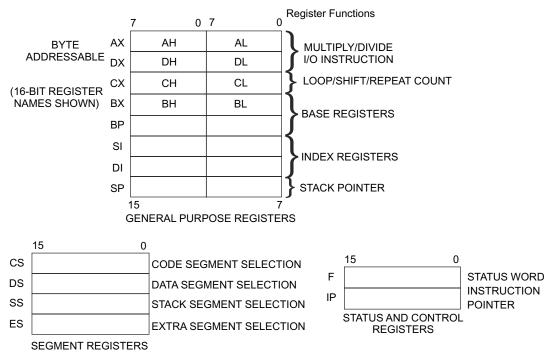

#### 5. Architecture of 8086 and 8088 Microprocessors

- 5.1 Introduction 147

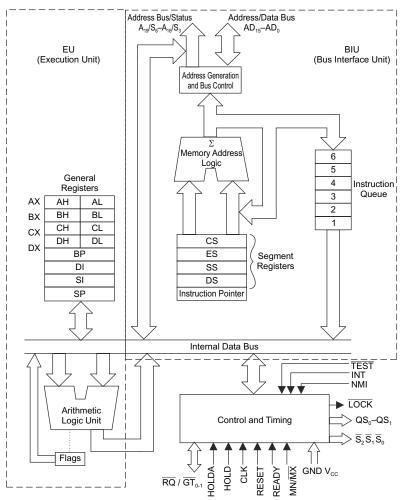

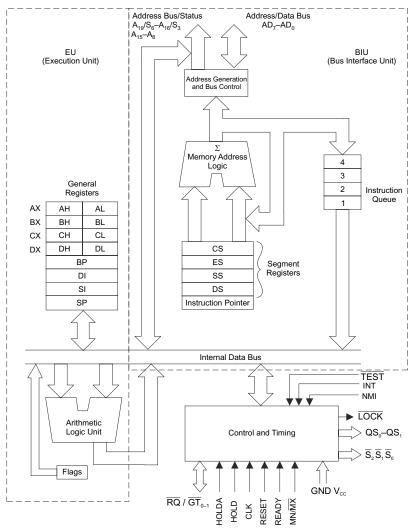

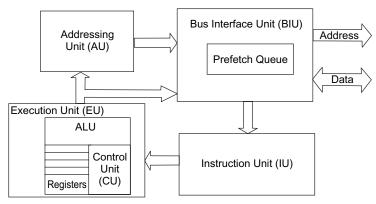

- 5.2 Architecture of 8086 149

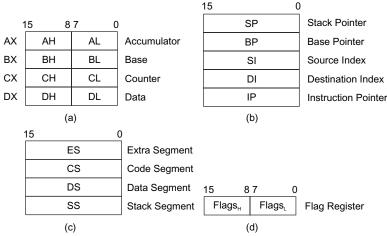

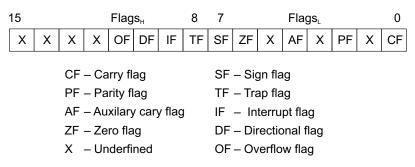

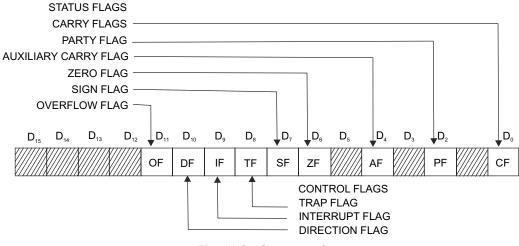

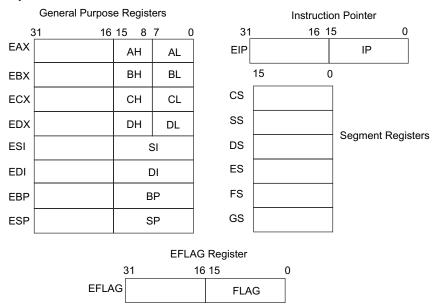

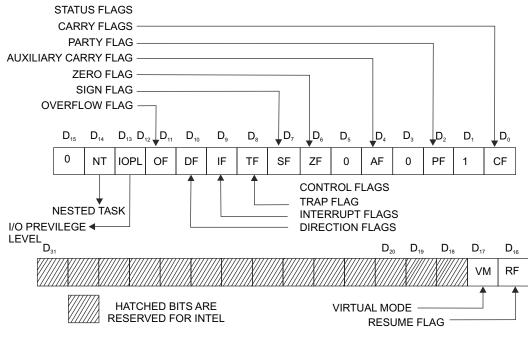

- 5.3 Registers 152

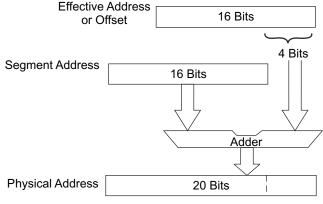

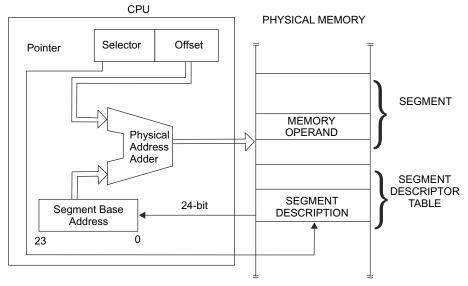

- 5.4 Logical And Physical Address 156

- 5.5 Address Bus, Data Bus, Control Bus 158

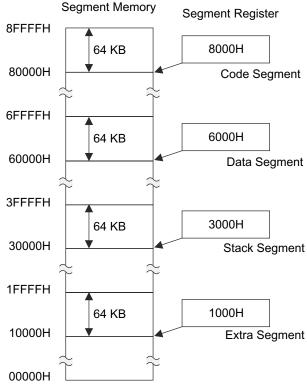

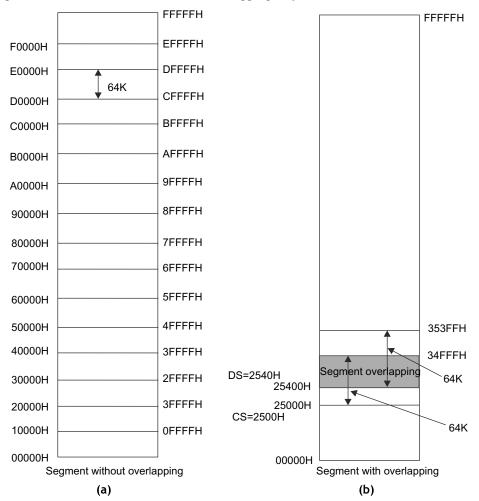

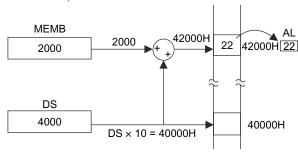

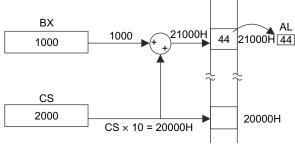

- 5.6 Memory Segmentation 158

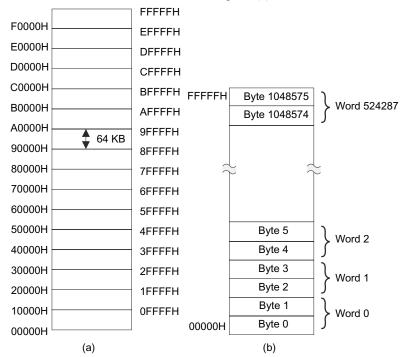

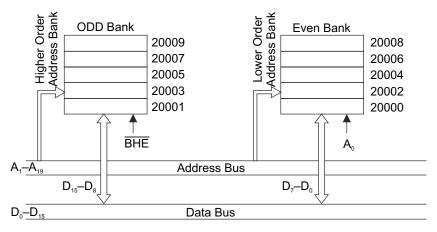

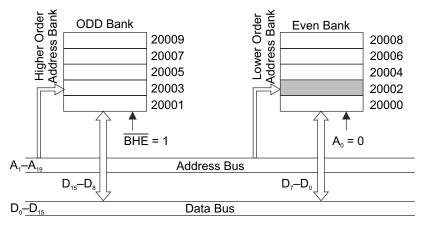

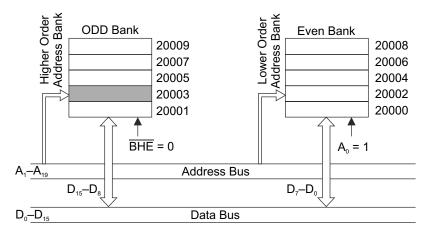

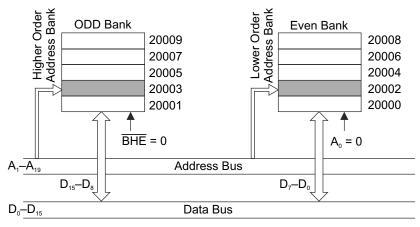

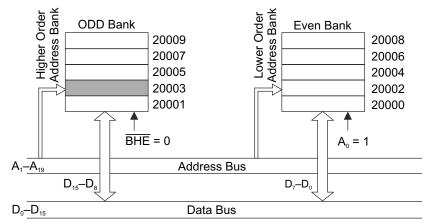

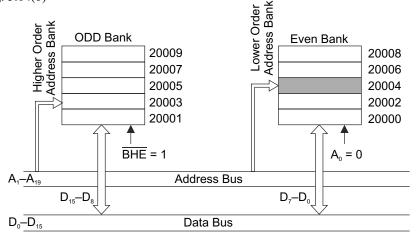

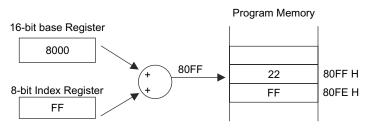

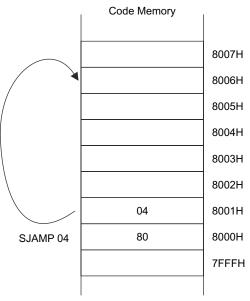

- 5.7 8086 Memory Addressing 160

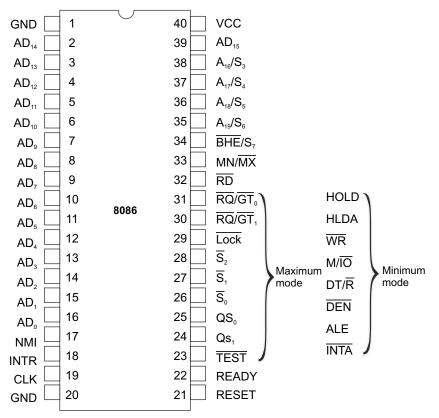

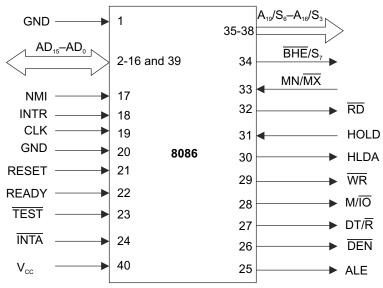

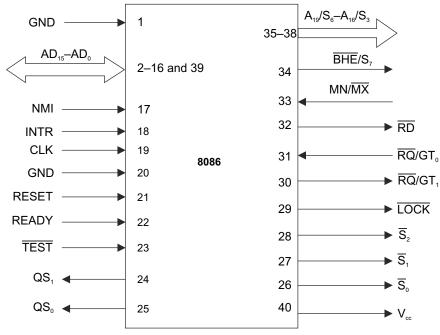

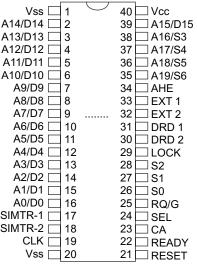

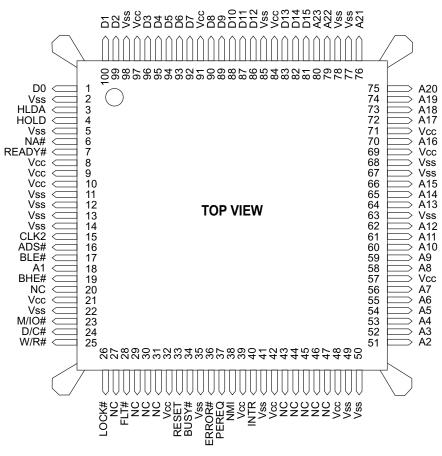

- 5.8 Pin Description of 8086 164

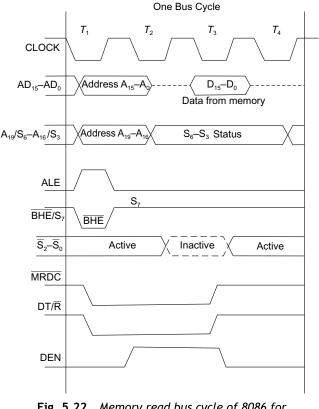

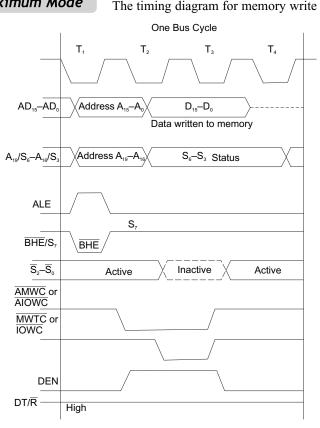

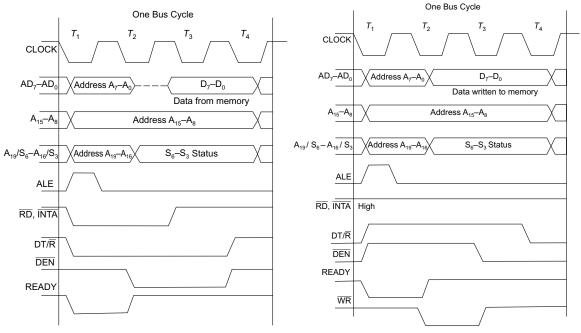

- 5.9 Memory Read and Write Bus Cycle of 8086 170

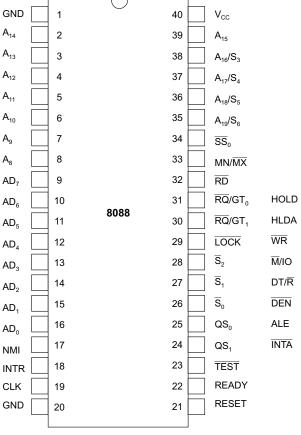

- 5.10 Intel 8088 Processor 176

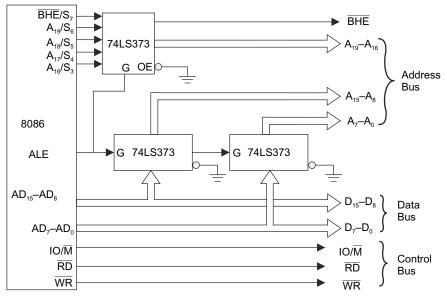

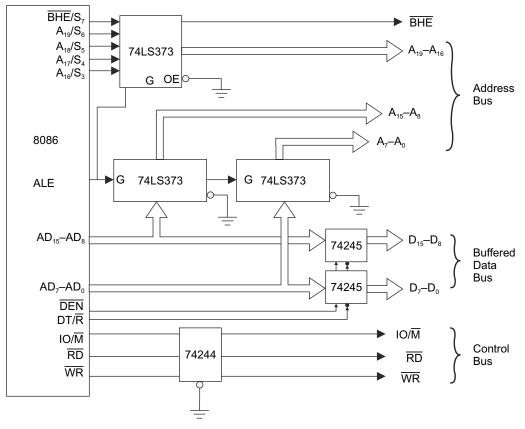

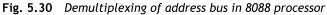

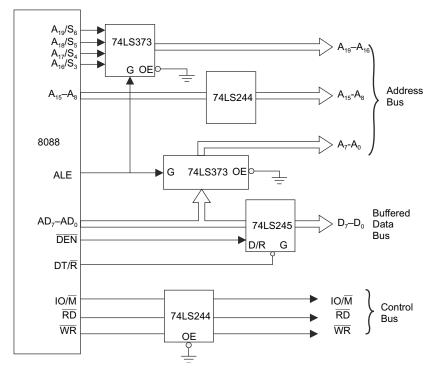

- 5.11 Demultiplexing of the System Bus in 8086 and 8088 Microprocessors 180

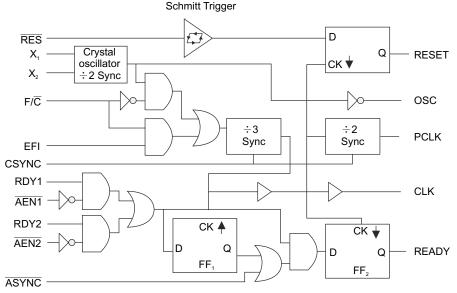

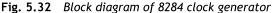

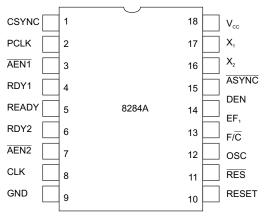

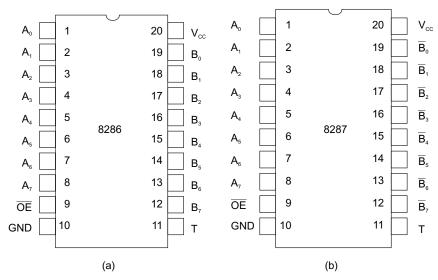

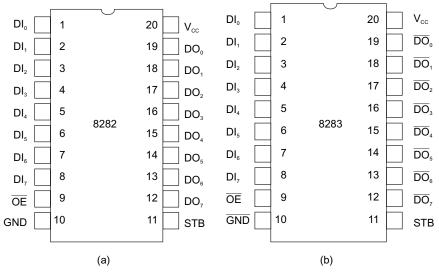

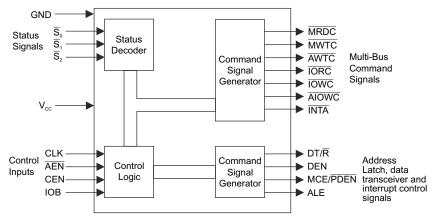

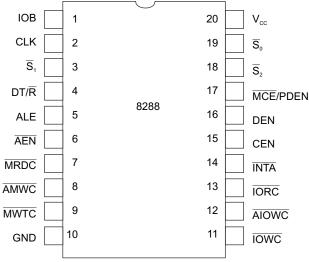

5.12 Some Important ICs: 8284A, 8286/8287, 8282/8283, and 8288 183

Summary 189

Multiple-Choice Questions 190

Short-Answer-Type Questions 190

Review Questions 191

Answers to Multiple-Choice Questions 191

viii

147

|    | Contents                                                                                                                                                                                  | ix  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

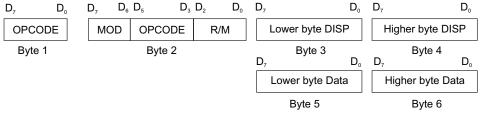

| 6. | <ul> <li>Instruction Set and Addressing Modes of the 8086 Microprocessor</li> <li>6.1 Introduction 192</li> <li>6.2 Addressing Modes 192</li> <li>6.3 8086 Instruction Set 203</li> </ul> | 192 |

|    | Summary 239<br>Multiple-Choice Questions 240<br>Short-Answer-Type Questions 241<br>Review Questions 241                                                                                   |     |

|    | Answers to Multiple-Choice Questions 242                                                                                                                                                  |     |

| 7. | Assembly-Language Programs of the 8086 Microprocessor and 8087, 80287<br>and 80387 Numeric Data Processors                                                                                | 243 |

|    | 7.1 Introduction 243                                                                                                                                                                      | 243 |

|    | 7.2 Assembly-Language Commands 246                                                                                                                                                        |     |

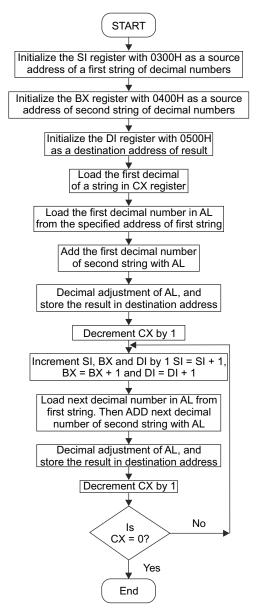

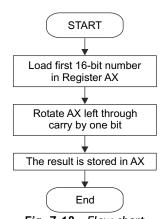

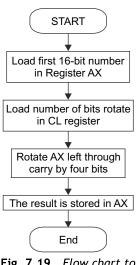

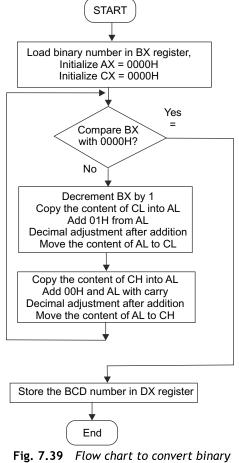

|    | 7.3 Assembly Language Programs 255                                                                                                                                                        |     |

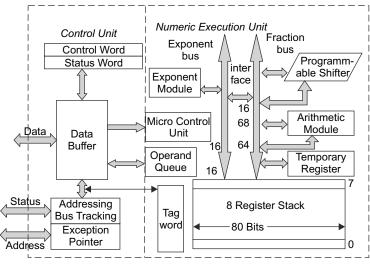

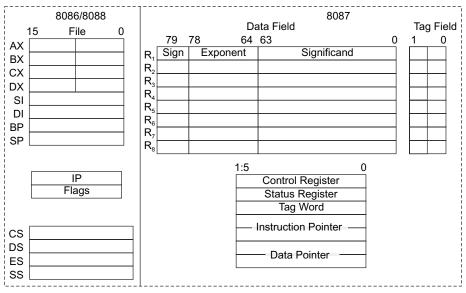

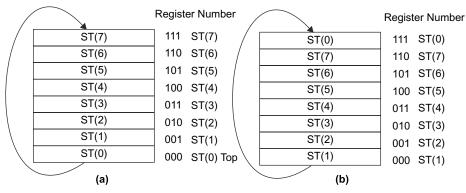

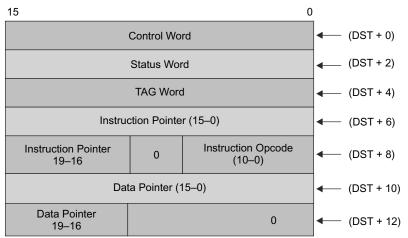

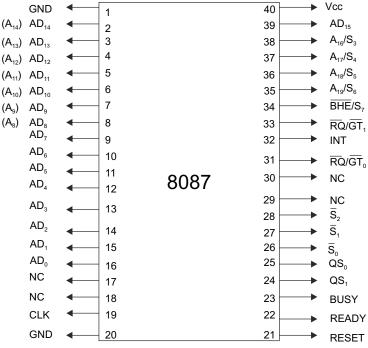

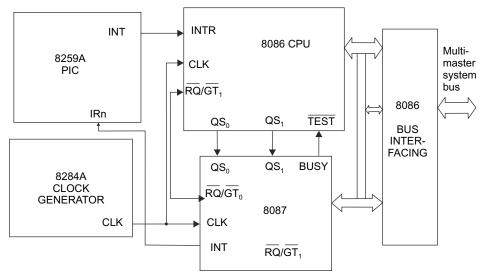

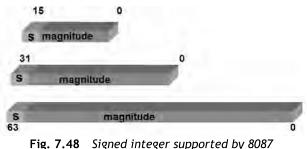

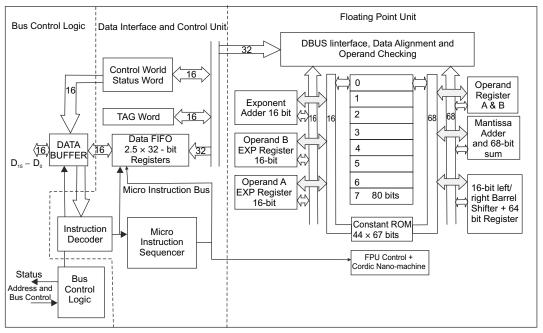

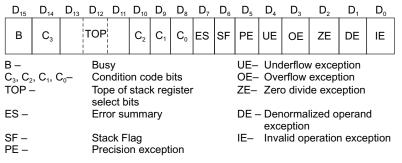

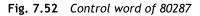

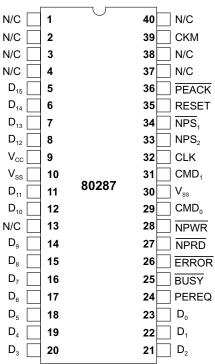

|    | 7.4 8087, 80287 And 80387 Numeric Data Processors 289                                                                                                                                     |     |

|    | 7.5 8087 Numeric Data Processor 289                                                                                                                                                       |     |

|    | 7.6 80287 Numeric Data Processor 303                                                                                                                                                      |     |

|    | 7.7 80387 Numeric Data Processor 307                                                                                                                                                      |     |

|    | Summary 308                                                                                                                                                                               |     |

|    | Multiple-Choice Questions 308                                                                                                                                                             |     |

|    | Short-Answer-Type Questions 310                                                                                                                                                           |     |

|    | Review Questions 310                                                                                                                                                                      |     |

|    | Answers to Multiple-Choice Questions 312                                                                                                                                                  |     |

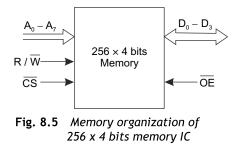

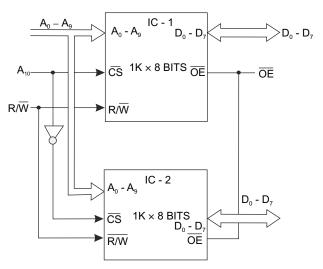

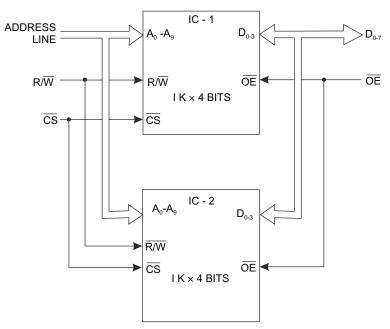

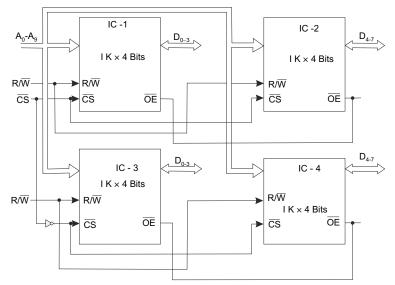

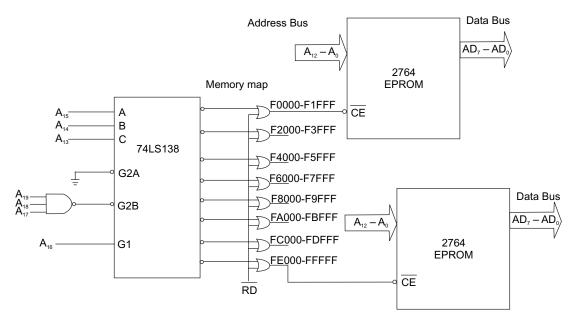

| 8. | I/O and Memory Interfacing Using 8085/8086                                                                                                                                                | 313 |

|    | 8.1 Introduction 313                                                                                                                                                                      |     |

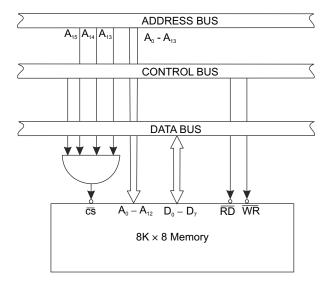

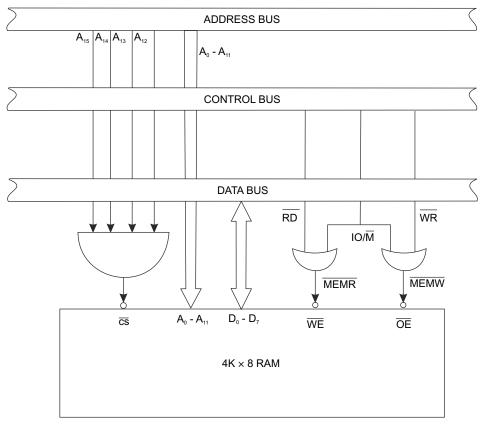

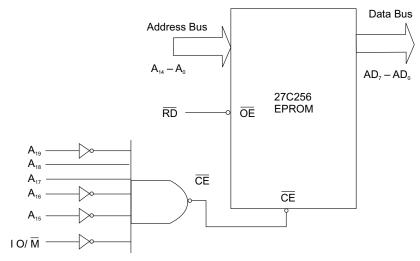

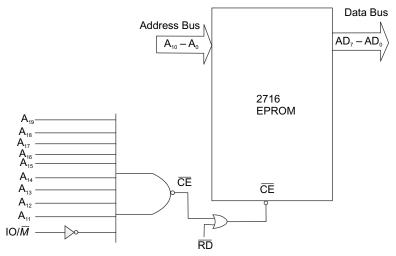

|    | 8.2 Memory Interfacing 313                                                                                                                                                                |     |

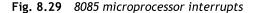

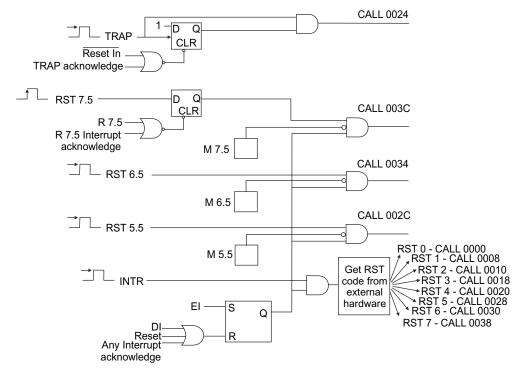

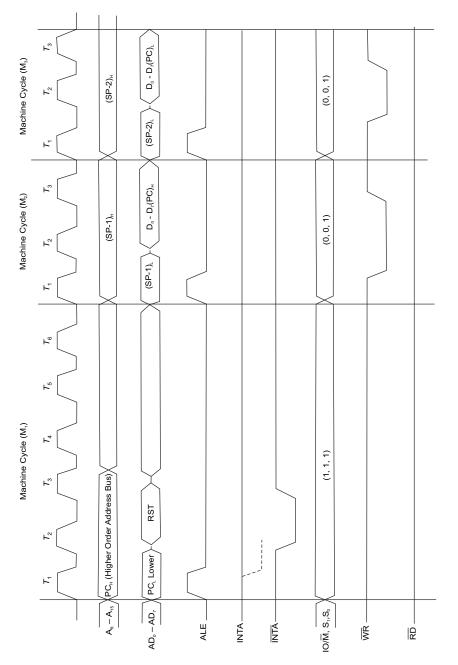

|    | 8.3 Interrupts of the 8085 Microprocessor 335                                                                                                                                             |     |

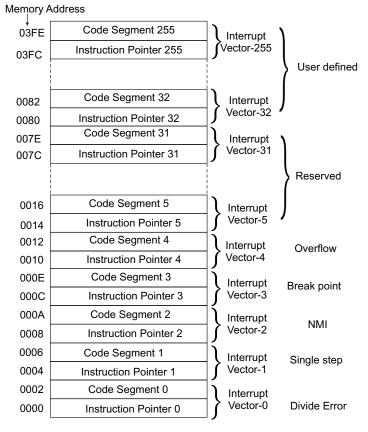

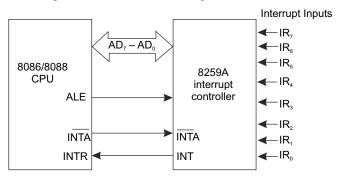

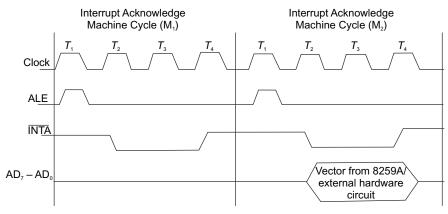

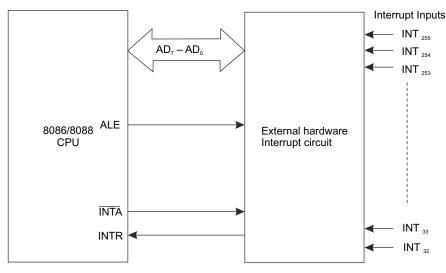

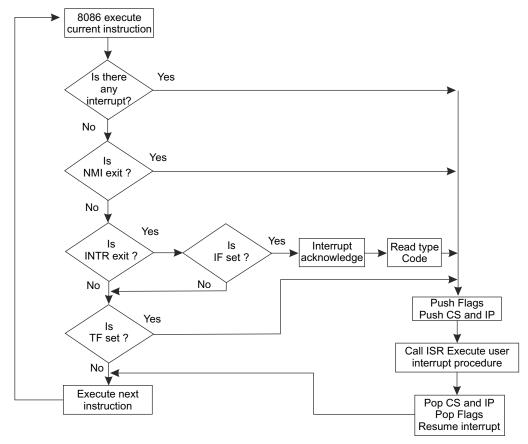

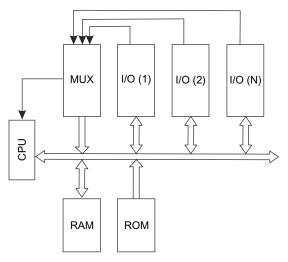

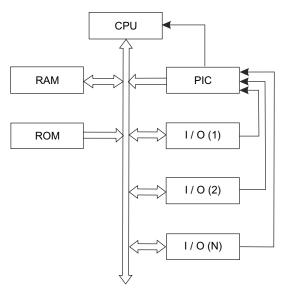

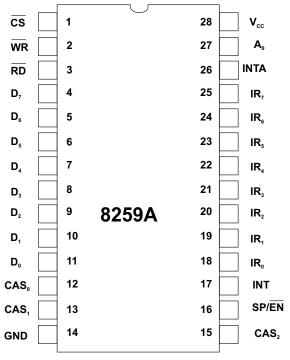

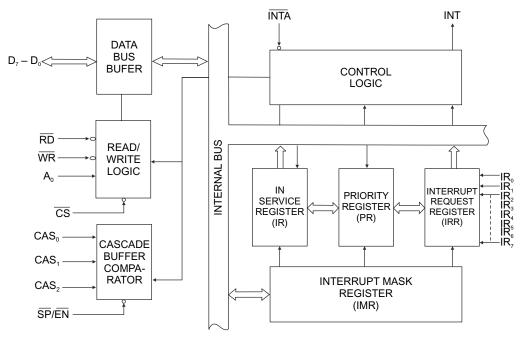

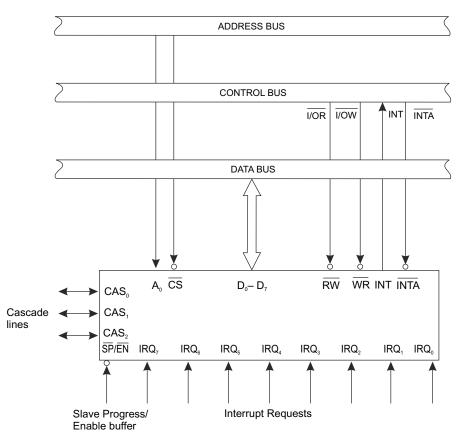

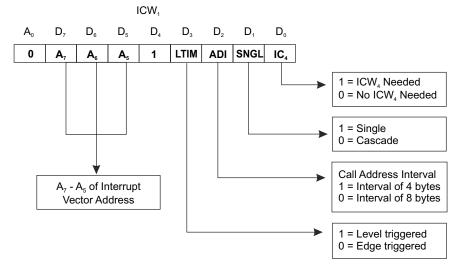

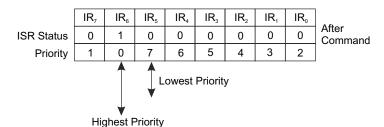

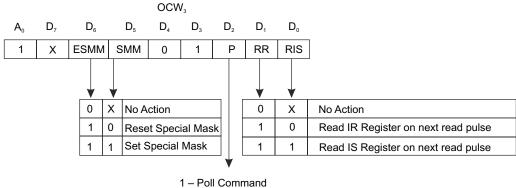

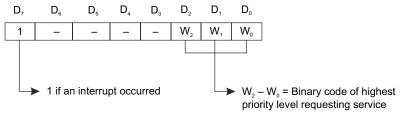

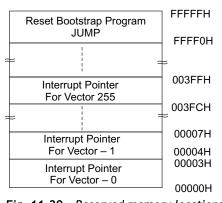

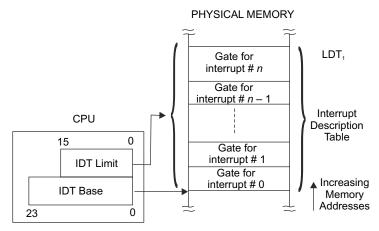

|    | <ul> <li>8.4 Interrupts of 8086/8088 Microprocessor 348</li> <li>8.5 8259A Programmable Interrupt Controller 355</li> </ul>                                                               |     |

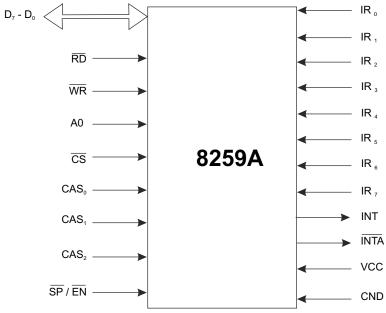

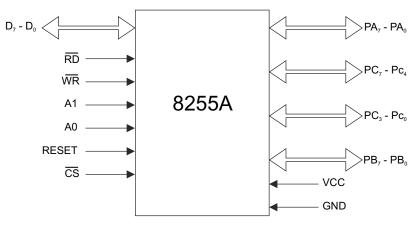

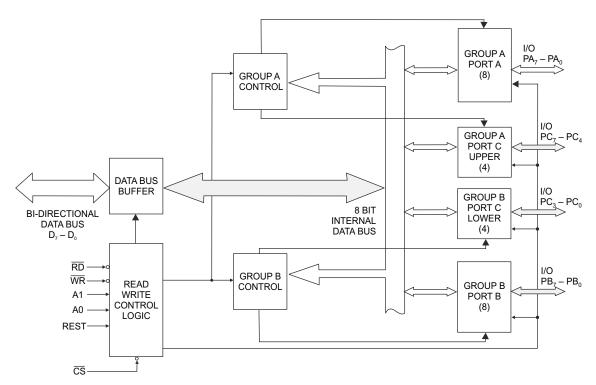

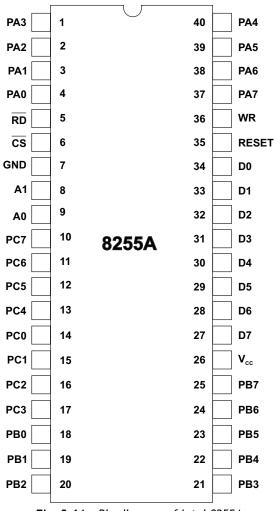

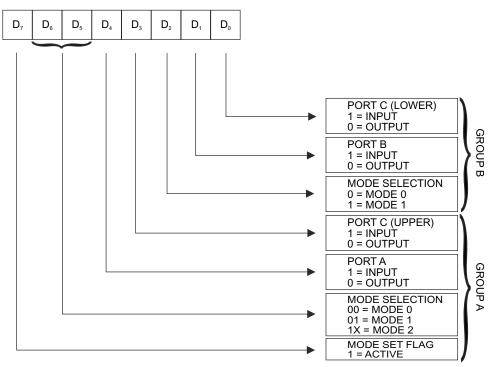

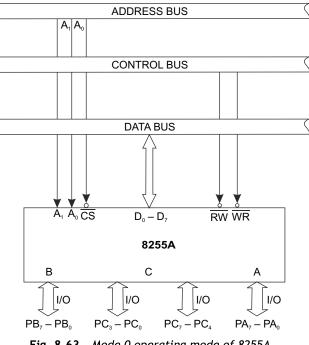

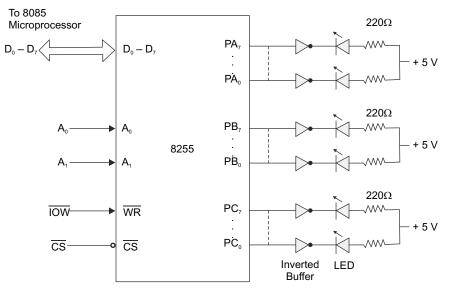

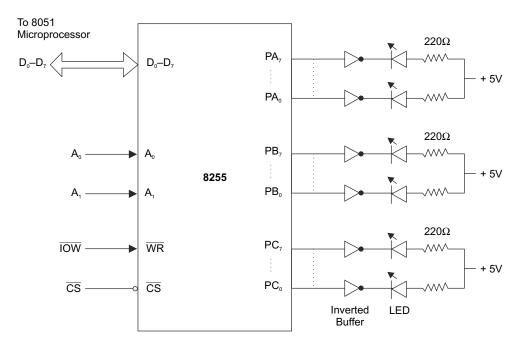

|    | <ul> <li>8.5 8259A Programmable Interrupt Controller 355</li> <li>8.6 Programmable Peripheral Interface, 8255 368</li> </ul>                                                              |     |

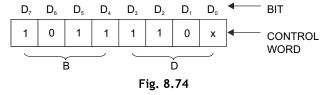

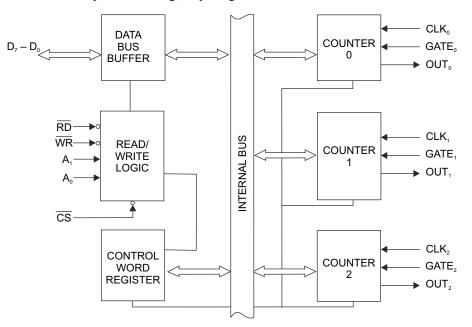

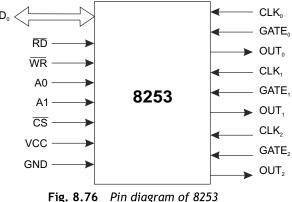

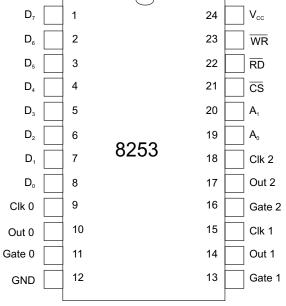

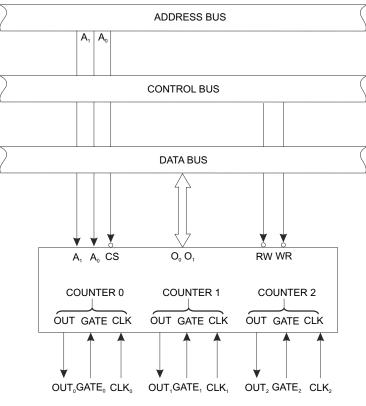

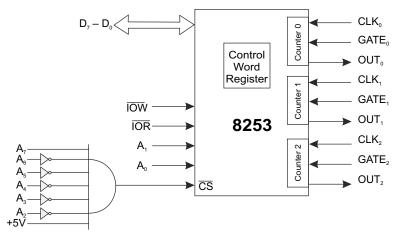

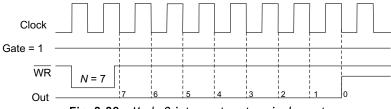

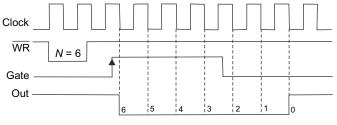

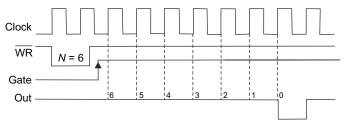

|    | 8.7 8253 Programmable Counter/Interval Timer 382                                                                                                                                          |     |

|    | Summary 397                                                                                                                                                                               |     |

|    | Multiple-Choice Questions 398                                                                                                                                                             |     |

|    | Short-Answer Type Questions 399                                                                                                                                                           |     |

|    | Review Questions 400                                                                                                                                                                      |     |

|    | Answers to Multiple-Choice Questions 403                                                                                                                                                  |     |

| 9. | Communication and Bus Interfacing with the 8085/8086 Microprocessor                                                                                                                       | 404 |

|    | 9.1 Introduction 404                                                                                                                                                                      |     |

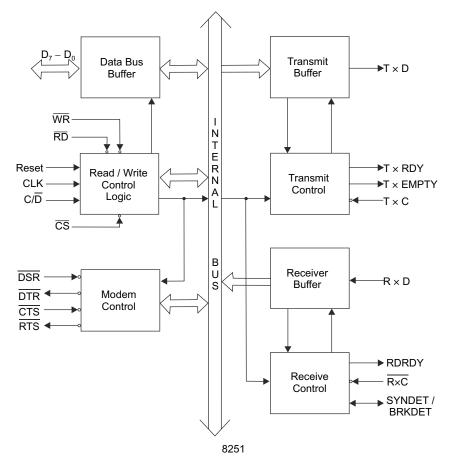

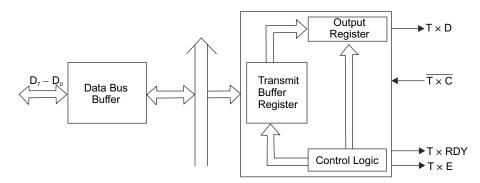

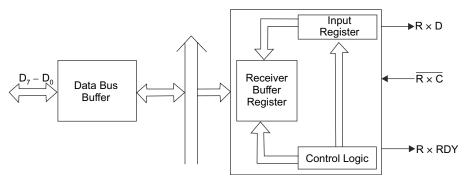

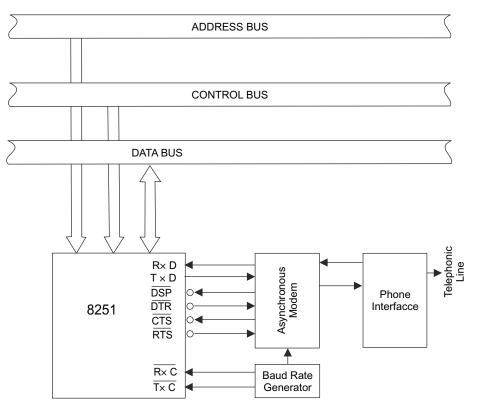

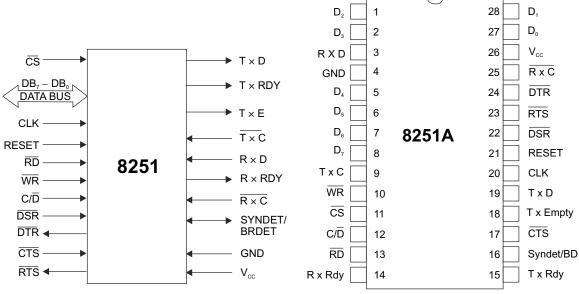

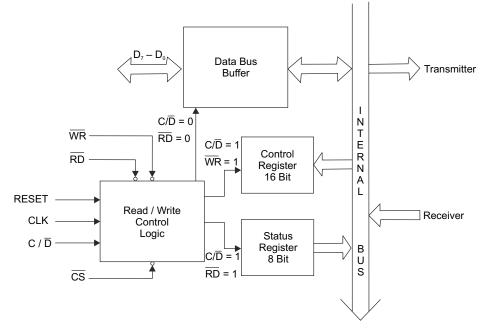

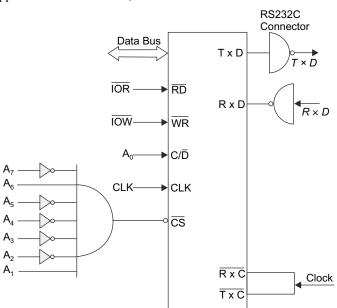

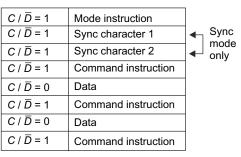

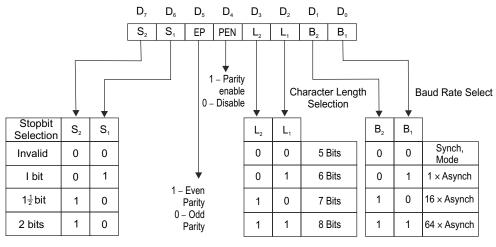

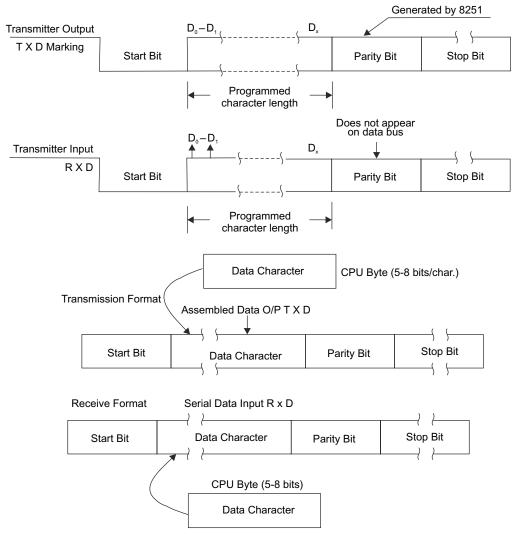

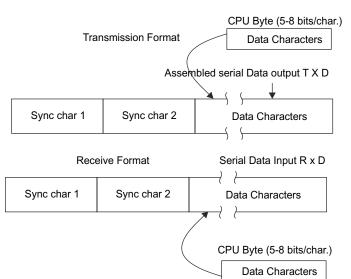

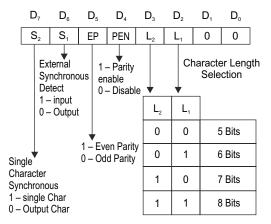

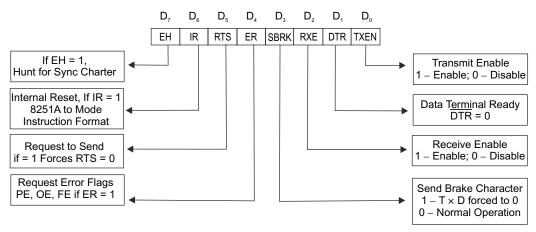

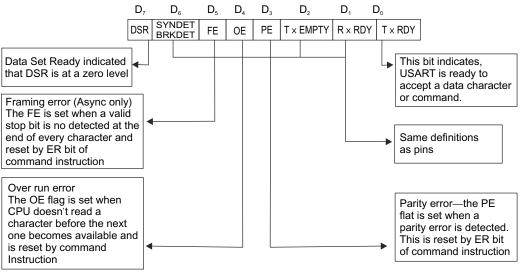

|    | 9.2 Serial Communication Interface 8251 404                                                                                                                                               |     |

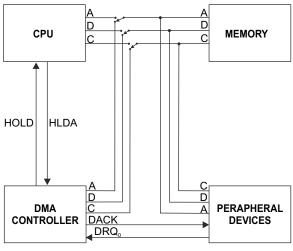

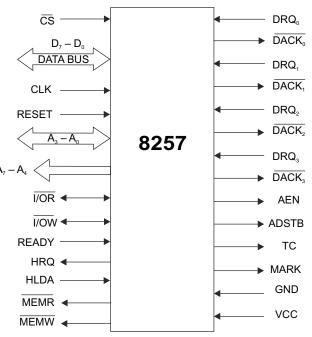

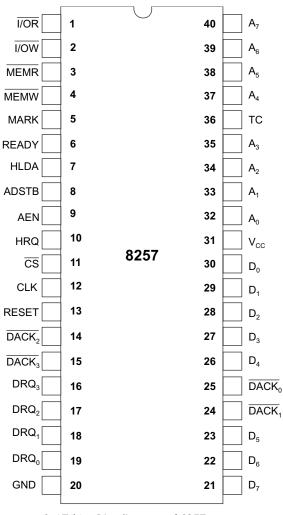

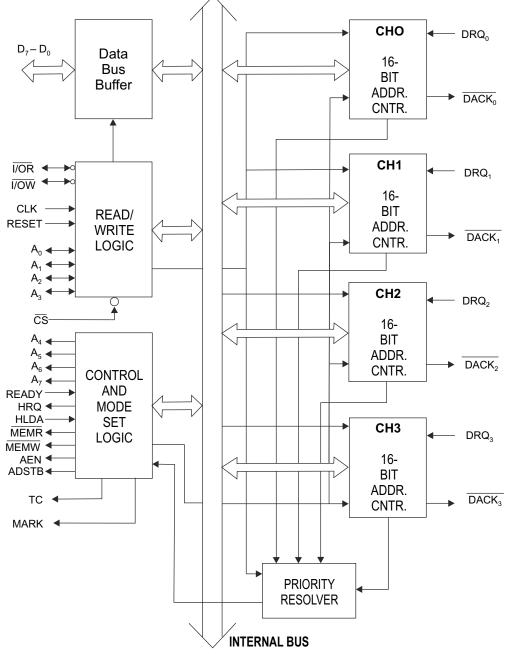

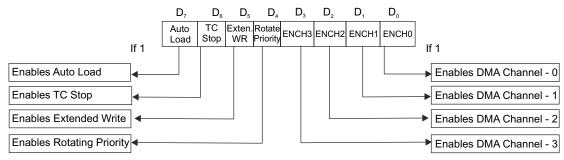

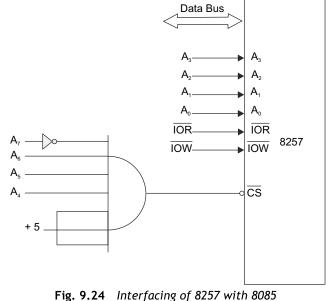

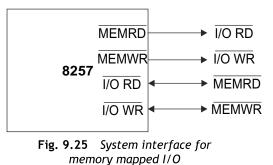

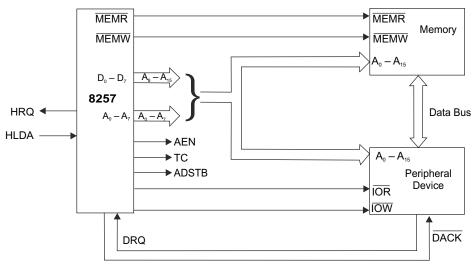

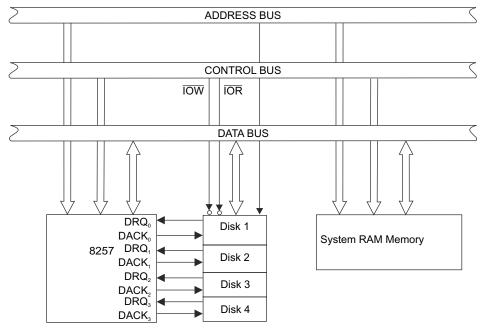

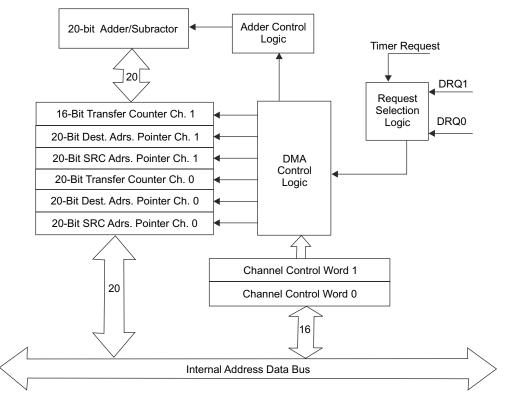

|    | 9.3 Direct Memory Access (Dma) Controller 8257 417                                                                                                                                        |     |

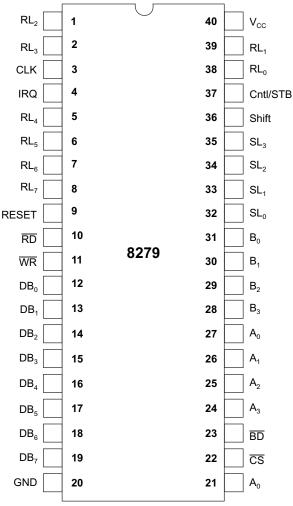

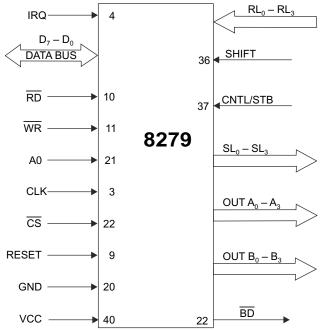

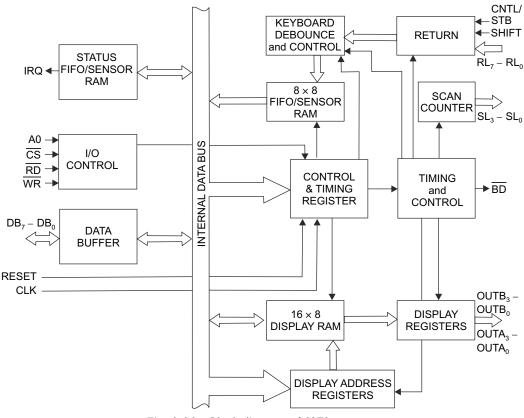

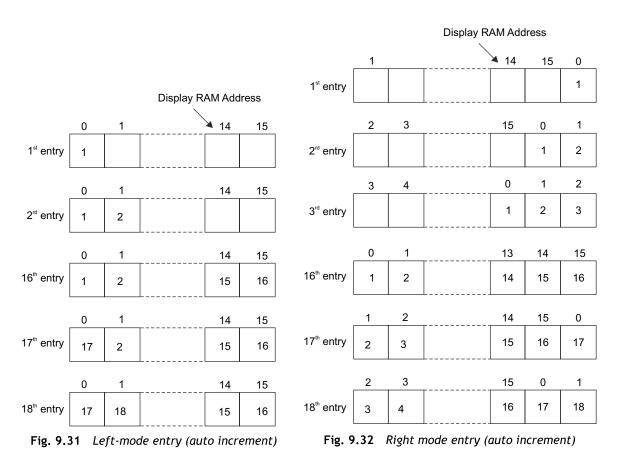

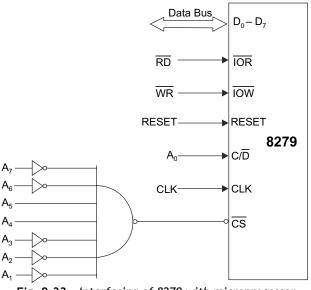

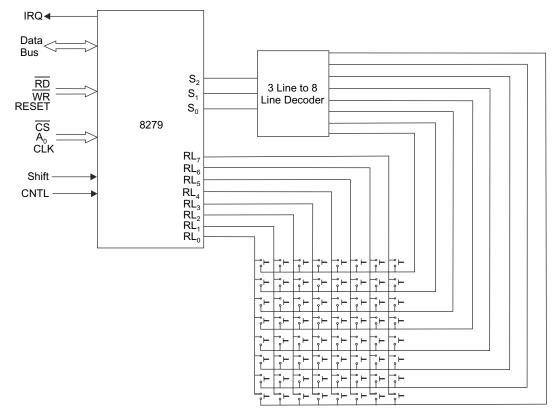

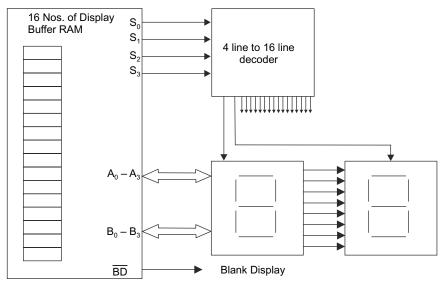

|    | 9.4 8279—Programmable Keyboard And Display I/O Interface 430                                                                                                                              |     |

х

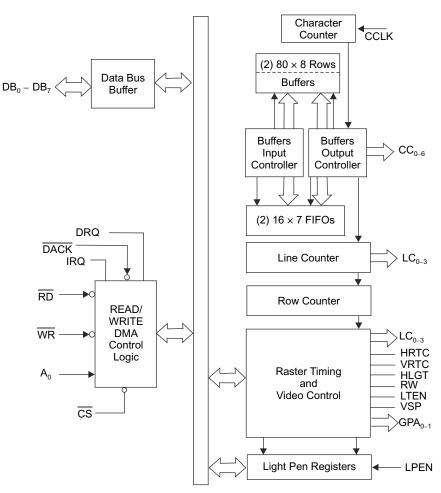

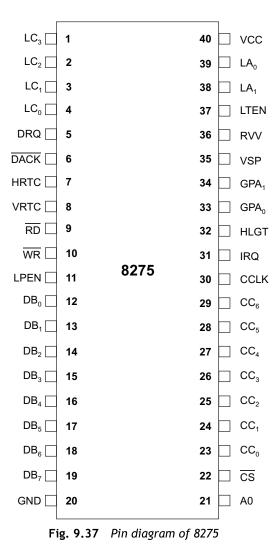

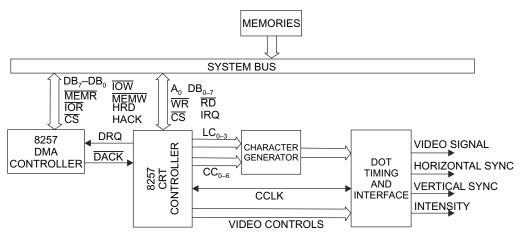

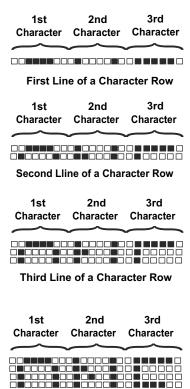

| 9.5   | 8275 Crt Controller 441                 |     |

|-------|-----------------------------------------|-----|

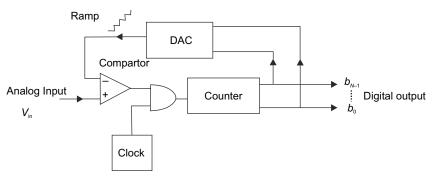

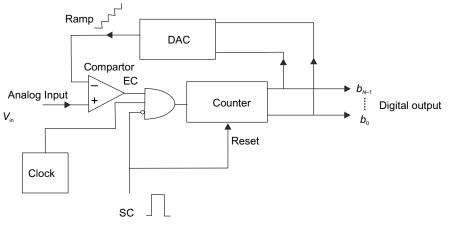

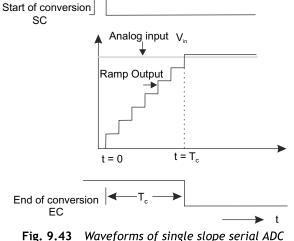

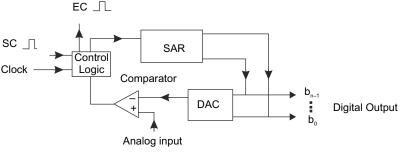

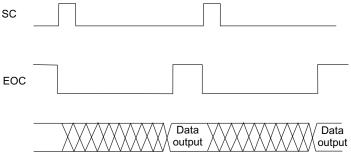

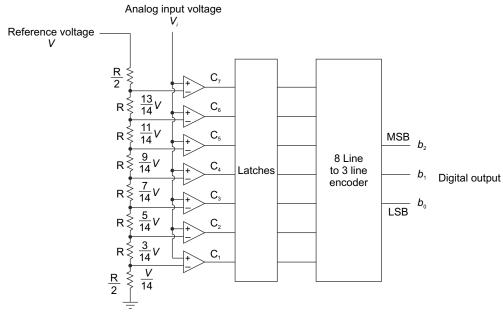

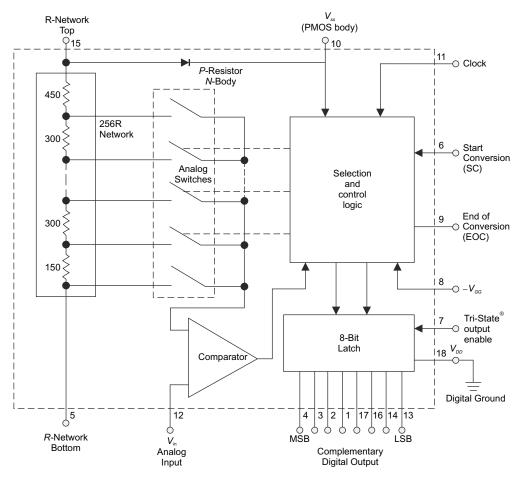

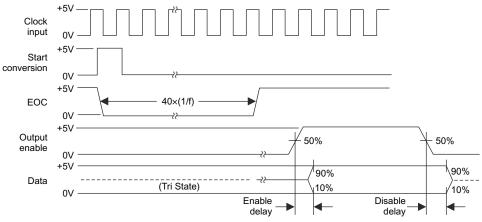

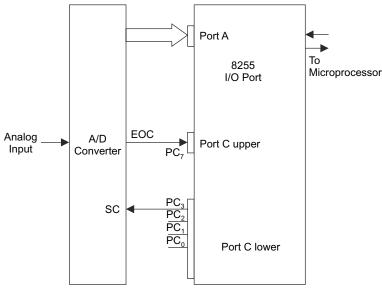

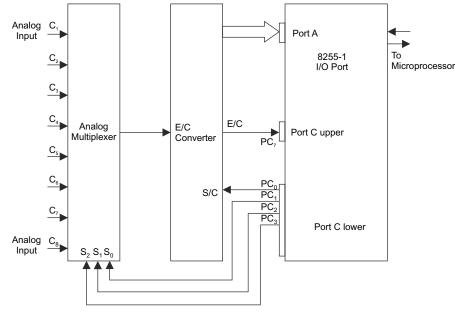

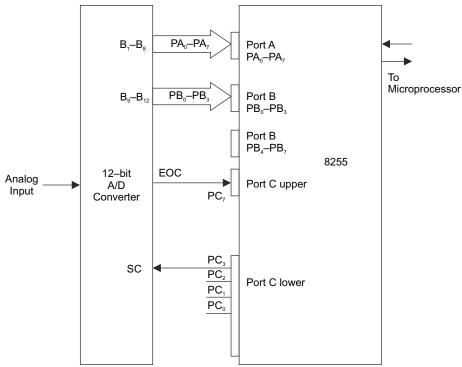

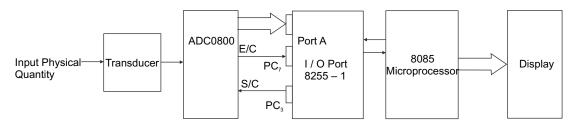

| 9.6   | Analog-to-Digital Converter Interfacing | 445 |

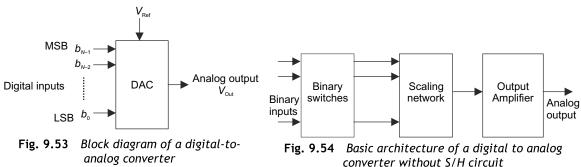

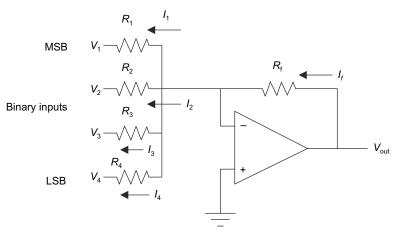

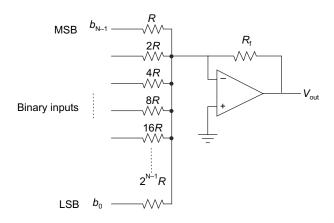

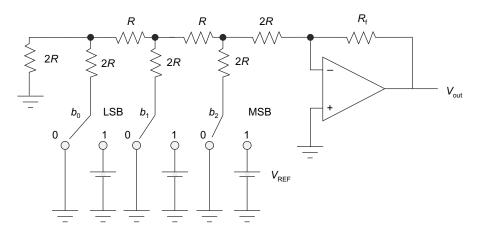

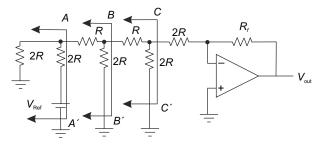

| 9.7   | Digital-to-Analog Converter Interfacing | 458 |

| 9.8   | Bus Interface 467                       |     |

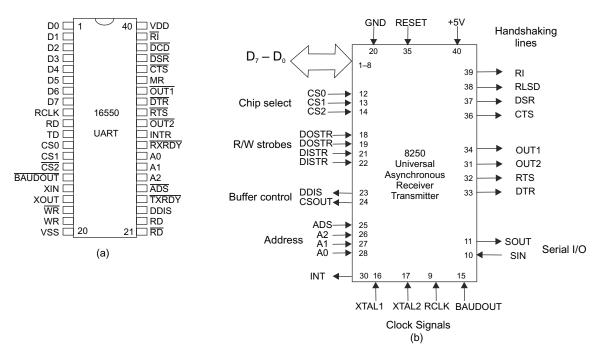

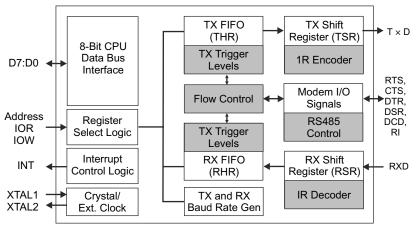

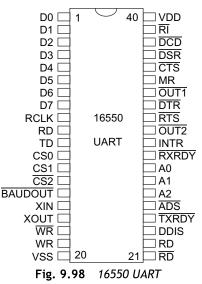

| 9.9   | 8250 Uart 480                           |     |

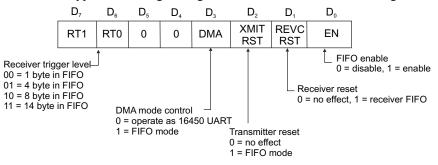

| 9.10  | 16550 Uart 485                          |     |

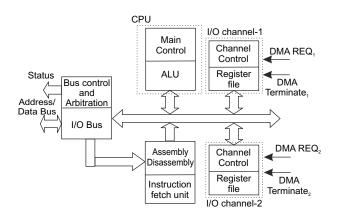

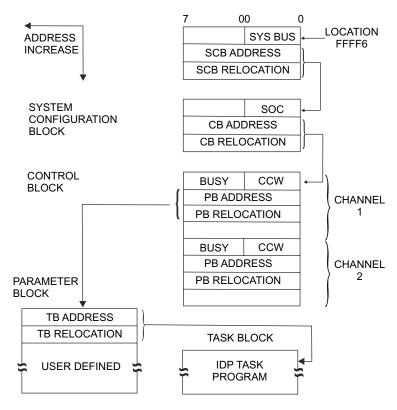

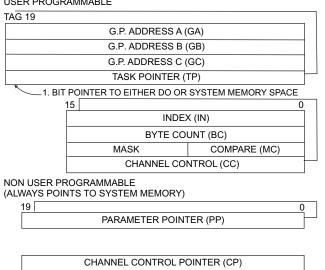

| 9.11  | 8089 I/O Processor 487                  |     |

| Summ  | nary 493                                |     |

| Multi | ple Choice Questions 493                |     |

| Short | -Answer Type Questions 495              |     |

| Revie | w Questions 496                         |     |

| Answ  | ers to Multiple-Choice Questions 498    |     |

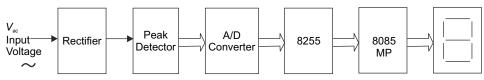

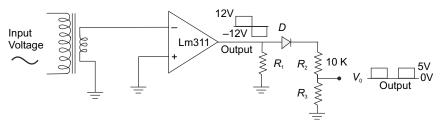

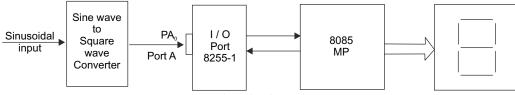

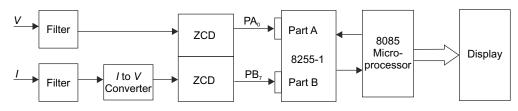

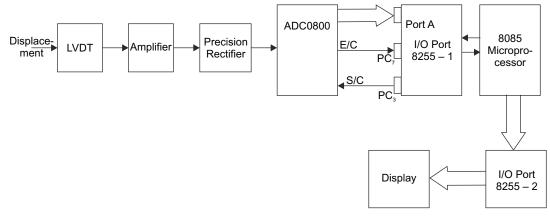

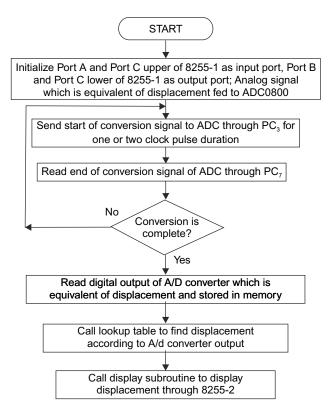

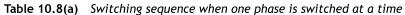

#### 10. Applications of 8085/8086 Microprocessors

- 10.1 Introduction 499

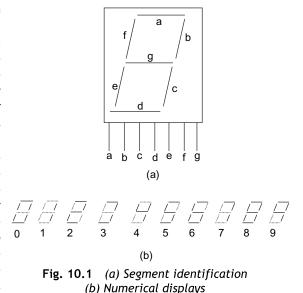

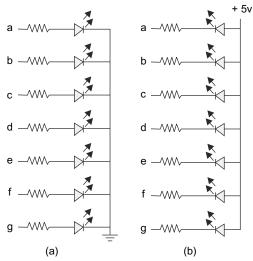

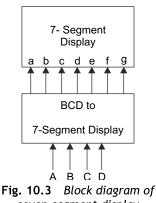

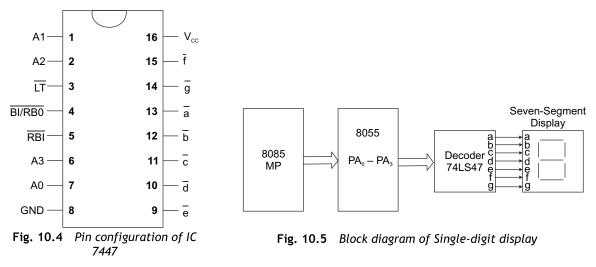

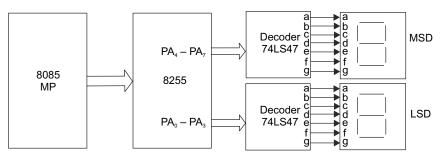

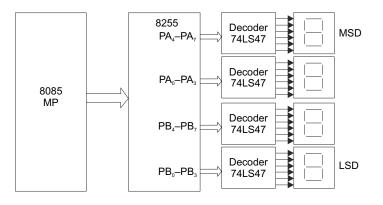

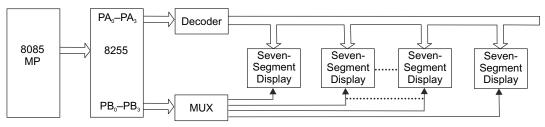

- 10.2 Seven-Segment Display 500

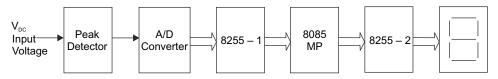

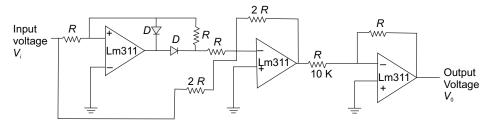

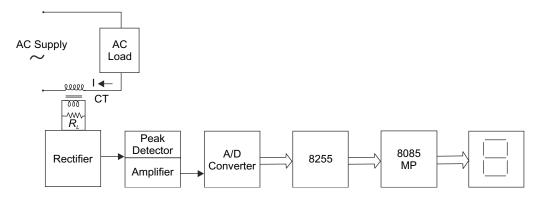

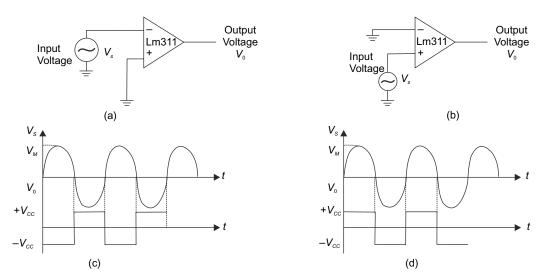

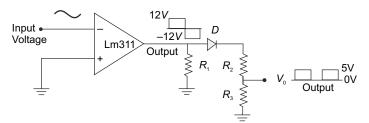

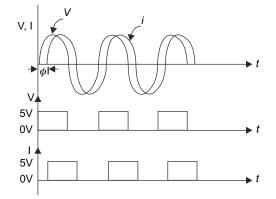

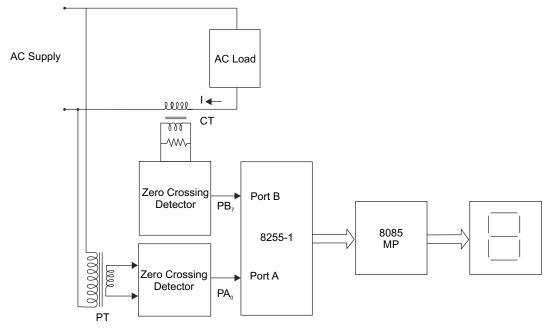

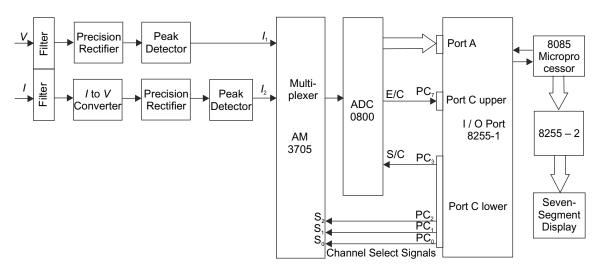

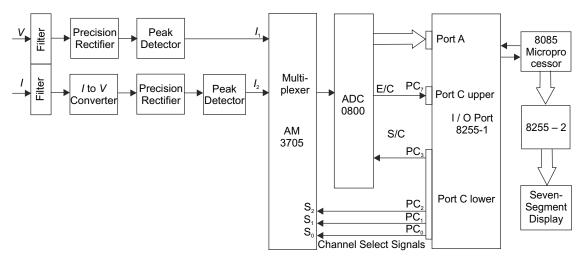

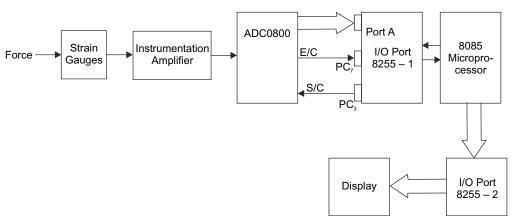

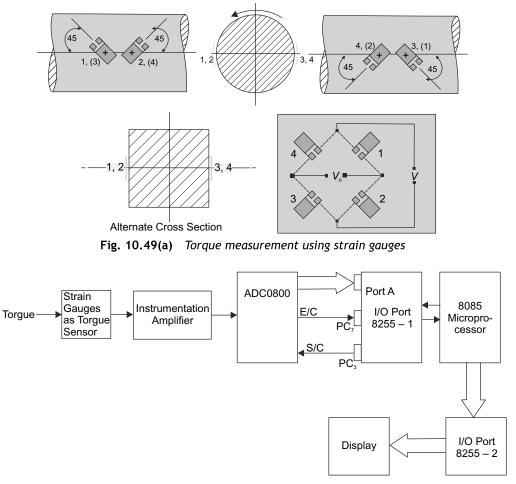

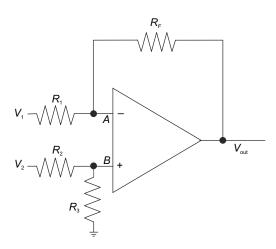

- 10.3 Measurement of Electrical Quantities 504

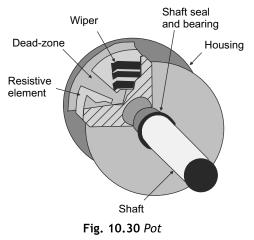

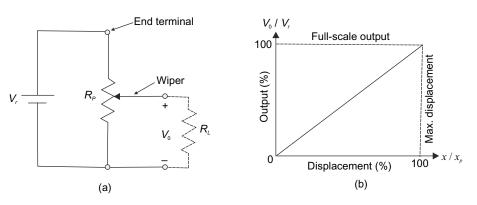

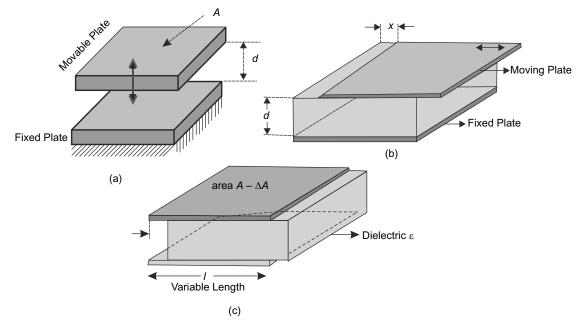

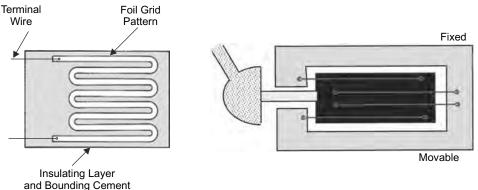

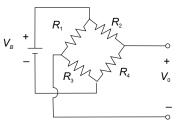

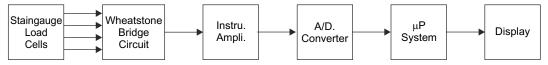

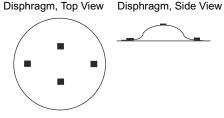

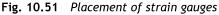

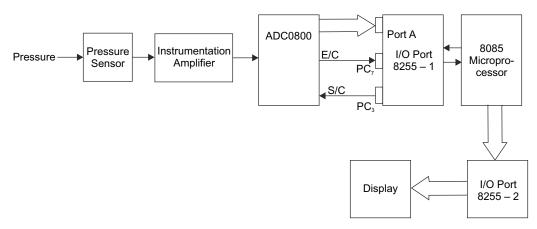

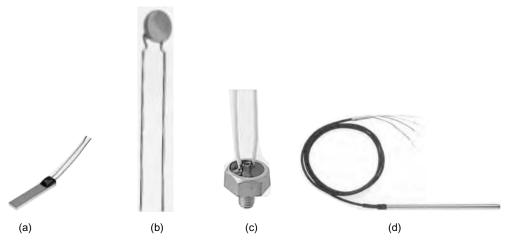

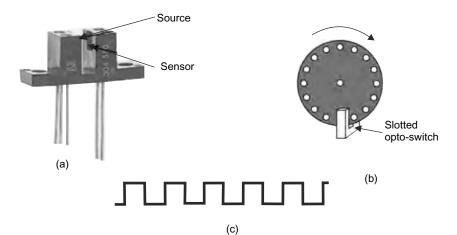

- 10.4 Measurement of Physical Quantities 528

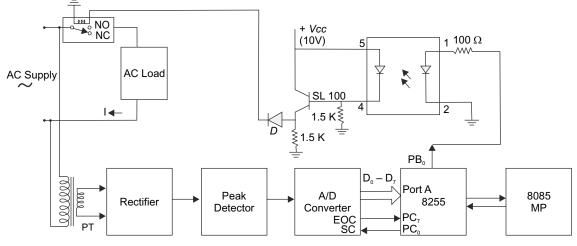

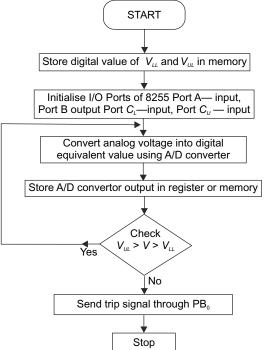

- 10.5 Microprocessor-Based Protection 549

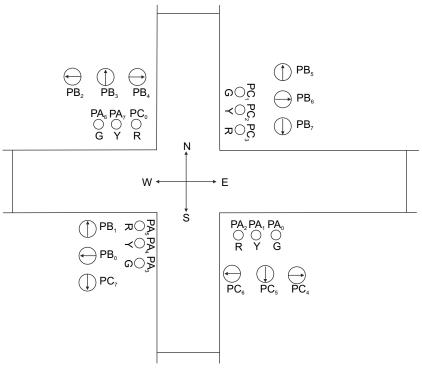

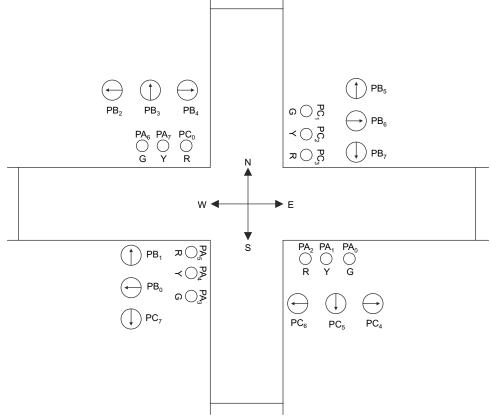

- 10.6 Microprocessor-Based Traffic Control 552

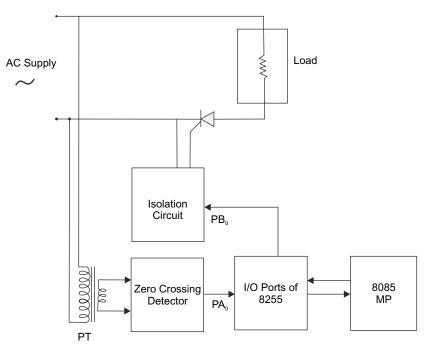

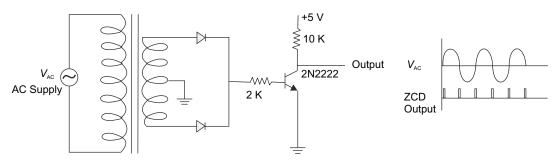

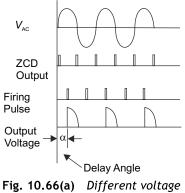

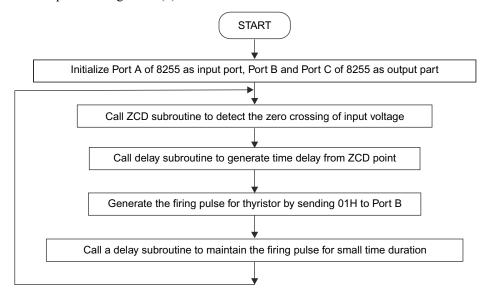

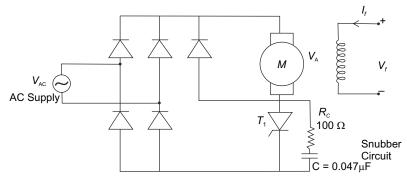

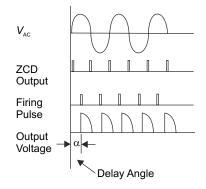

- 10.7 Microprocessor-Based Firing Circuit of A Thyristor 558

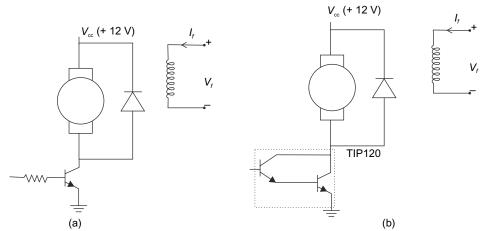

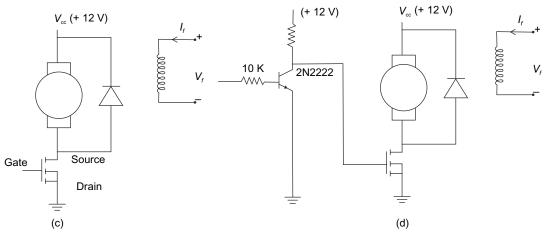

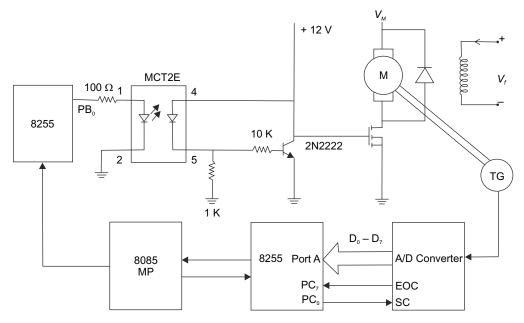

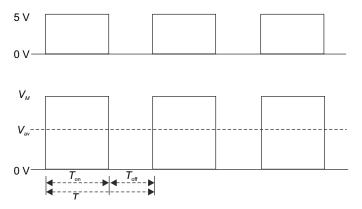

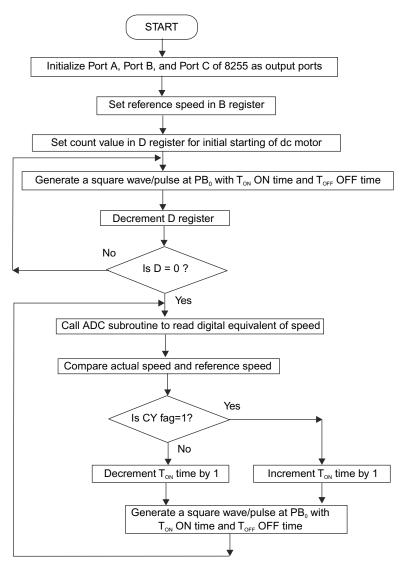

- 10.8 Speed Control of DC Motor 562

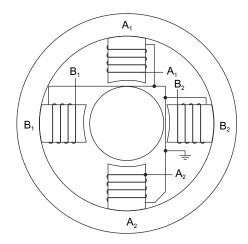

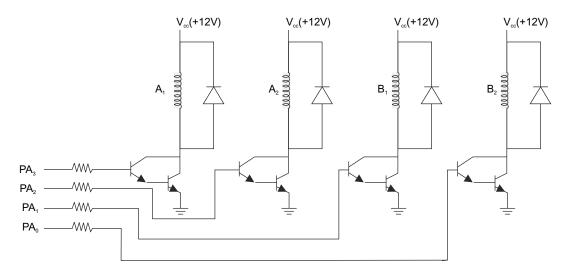

- 10.9 Stepper Motor 569

Summary 575

Multiple-Choice Questions 575

Short Answer Questions 576

Review Questions 576

Answers to Multiple-Choice Questions 578

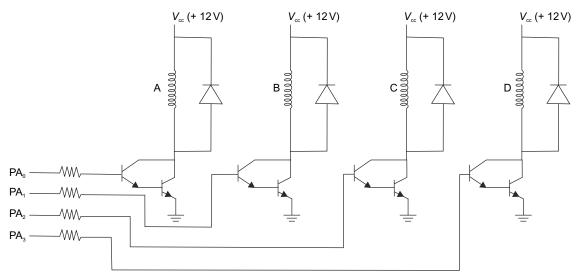

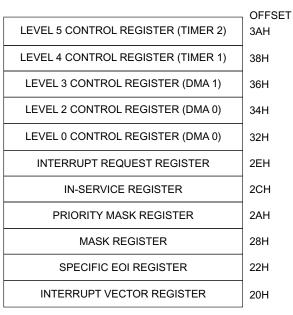

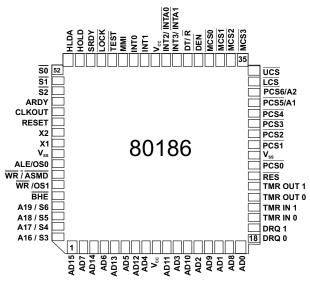

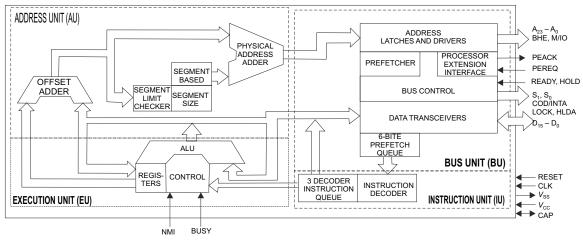

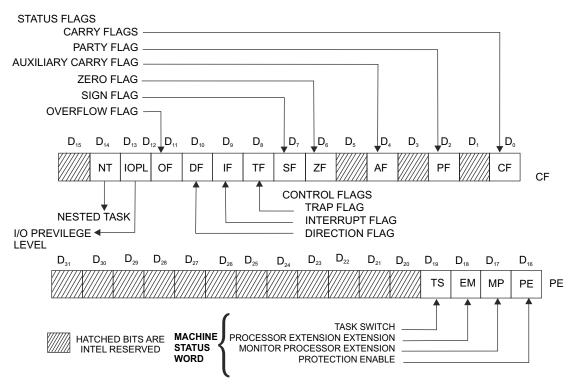

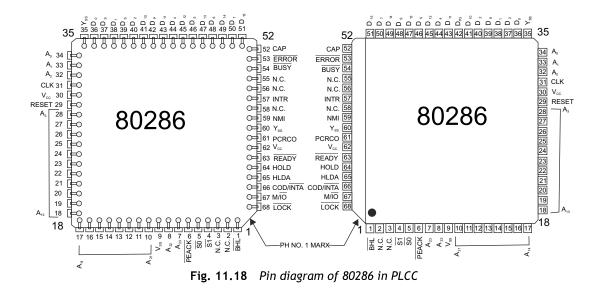

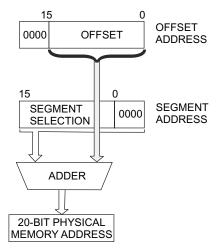

#### 11. 80186, 80286, 80386 and 80486 Microprocessors

- 11.1 Introduction 579

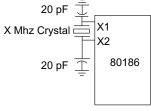

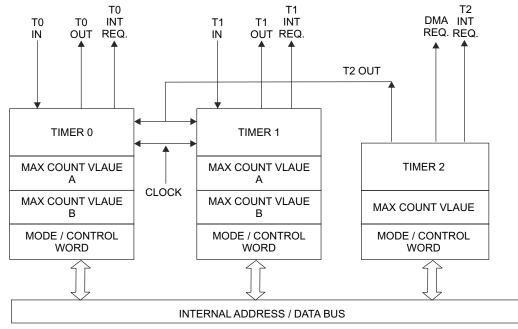

- 11.2 80186 Microprocessor Architecture 579

- 11.3 Pin Description of 80186 594

- 11.4 Addressing Modes of 80186 598

- 11.5 Data Types of 80186 598

- 11.6 Instruction Set of 80186 599

- 11.7 Comparison Between 8086 and 80186 601

- 11.8 Introduction to 80286 601

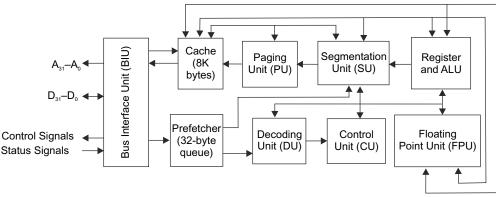

- 11.9 Architecture of 80286 602

- 11.10 Pin Diagram of 80286 606

- 11.11 Addressing Modes of 80286 609

- 11.12 Data Types of 80286 610

- 11.13 80286 Instruction Set 610

579

#### 499

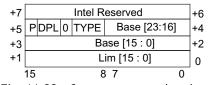

11.14 80286 Addressing Mode 614

11.15 Comparison Between 8086 and 80286 620

- 11.16 Comparison Between 80186 and 80286 621

- 11.17 Introduction to 80386 622

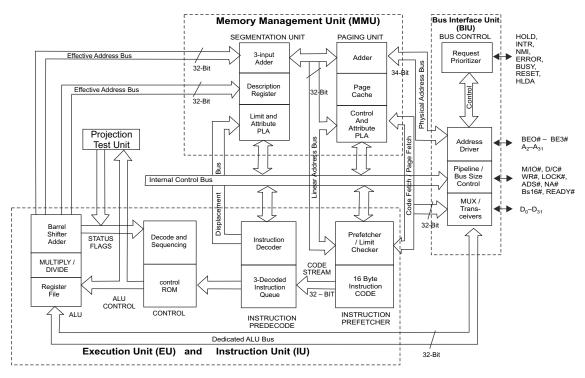

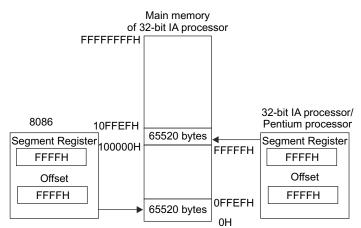

- 11.18 Architecture of 80386 623

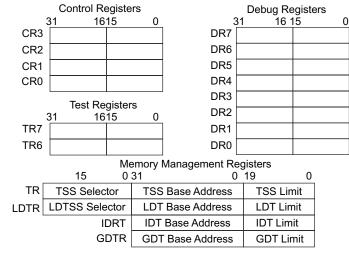

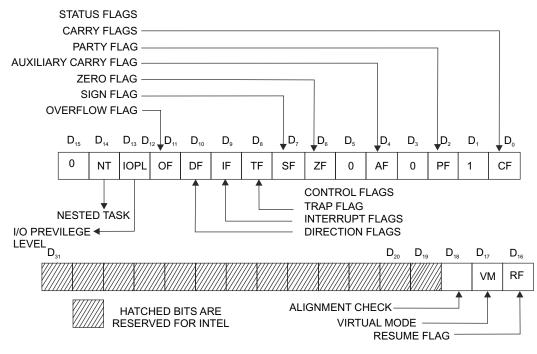

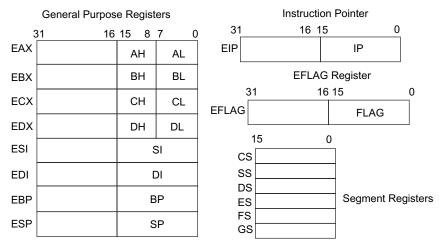

- 11.19 Registers of 80386 624

- 11.20 Pin Functions of 80386 628

- 11.21 Addressing Modes of 80386 630

- 11.22 Data Types of 80386 631

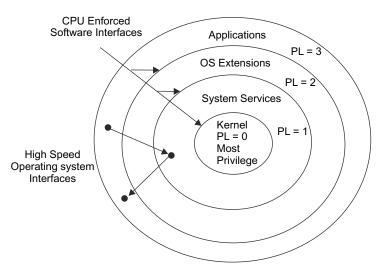

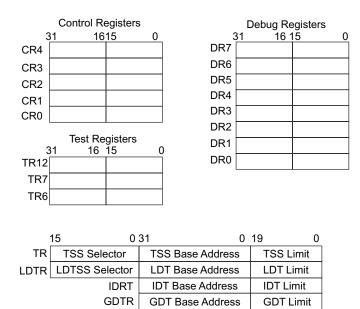

- 11.23 Operating Mode of 80386 631

- 11.24 Instruction Set 638

- 11.25 Comparison Between 80286 And 80386 639

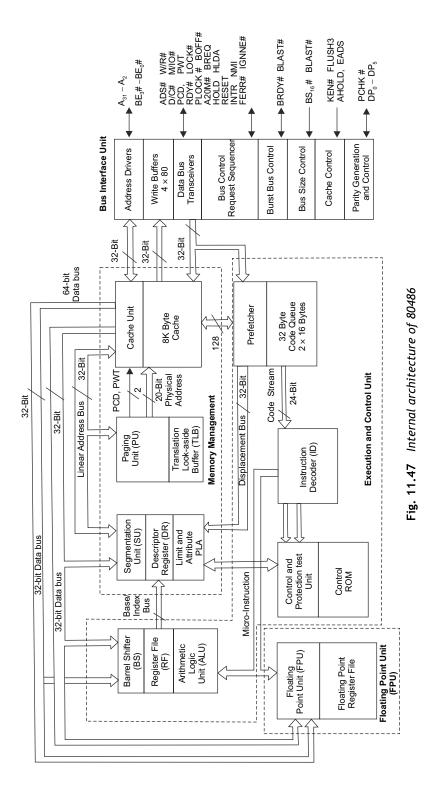

- 11.26 Introduction to 80486 640

- 11.27 Architecture of 80486 640

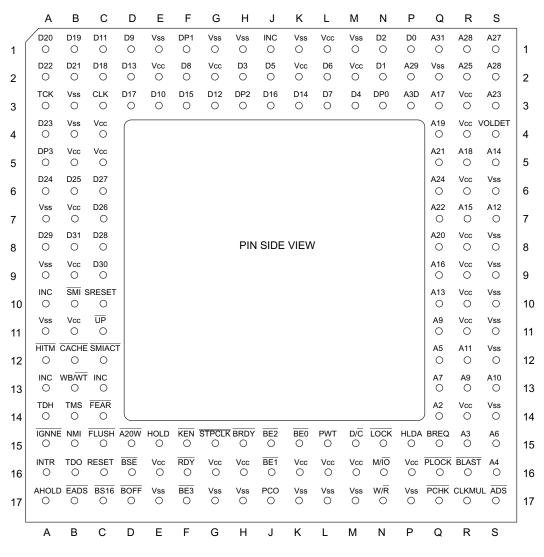

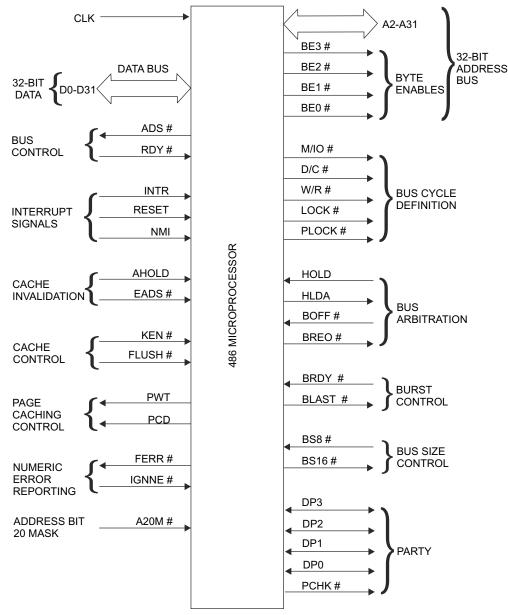

- 11.28 Pin Descriptions of 80486 643

- 11.29 Comparison Between 80386 And 80486 648

Summary 648

Multiple-Choice Questions 649

Short-Answer Questions 650

Review Questions 650

Answers to Multiple-Choice Questions 652

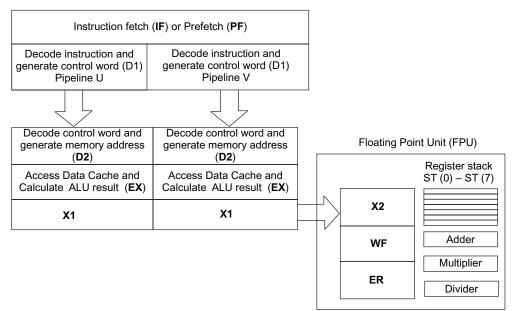

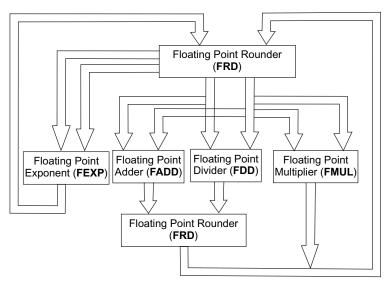

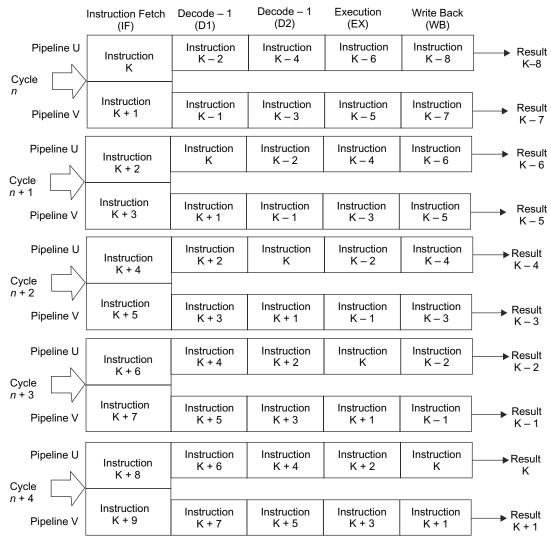

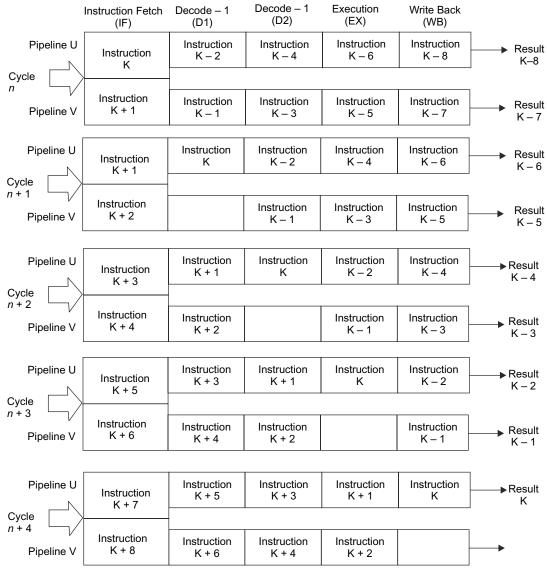

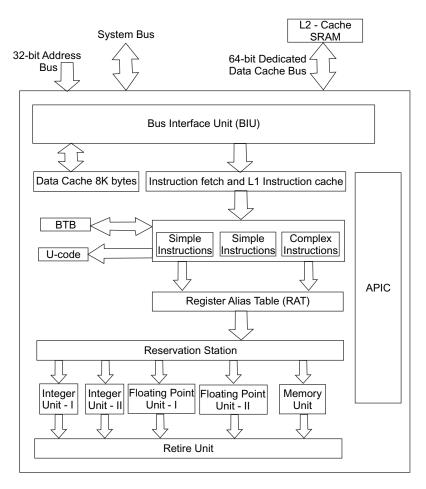

#### 12. Pentium and RISC Processors

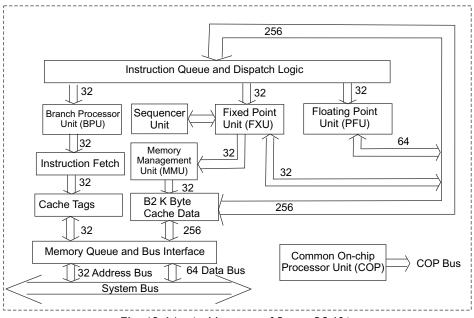

- 12.1 Introduction 653

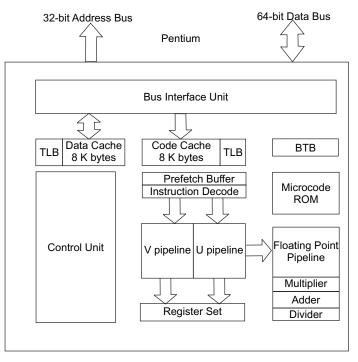

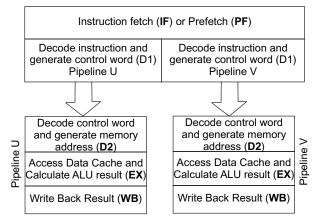

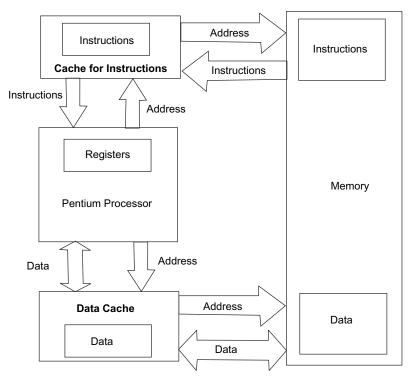

- 12.2 Pentium Internal Architecture 653

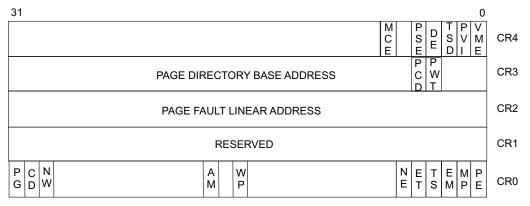

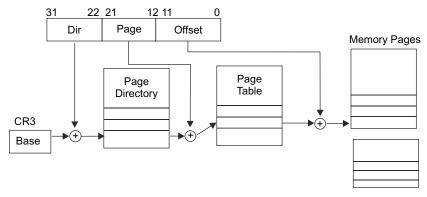

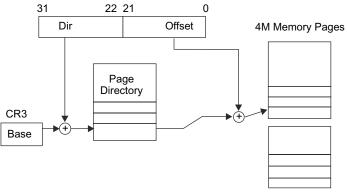

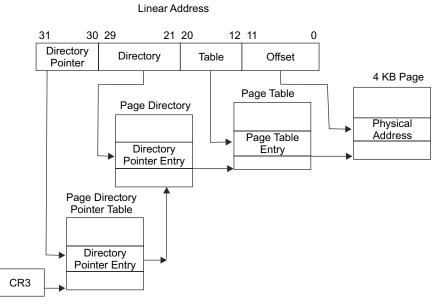

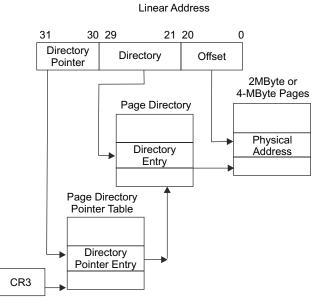

- 12.3 Pentium Operating Modes 662

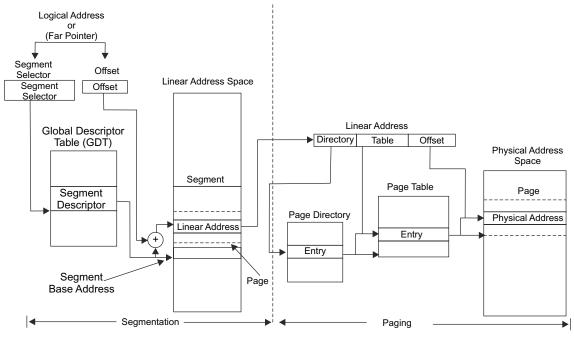

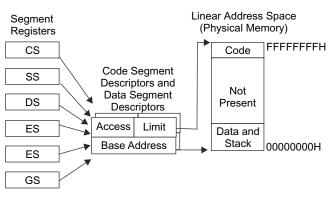

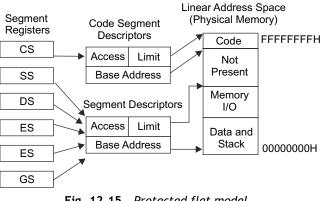

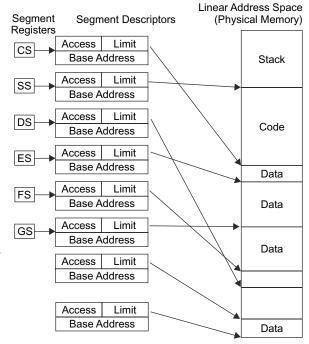

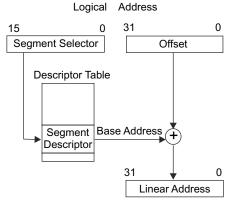

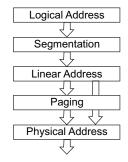

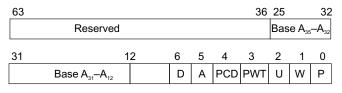

- 12.4 Segmentation 665

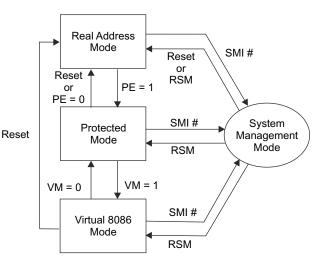

- 12.5 Physical, Linear and Logical Address 666

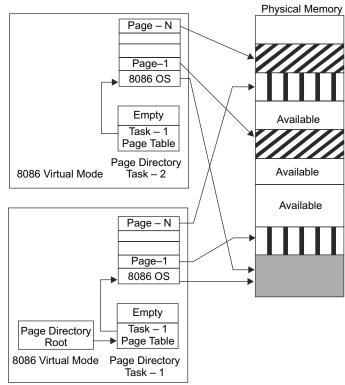

- 12.6 Virtual 8086 Mode 670

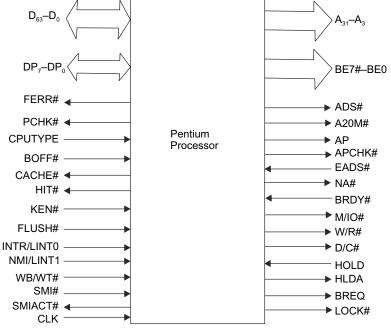

- 12.7 Pin Description of Pentium Processor 673

- 12.8 Addressing Modes of The Pentium Processor 676

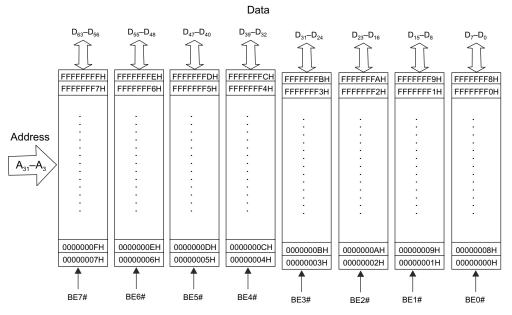

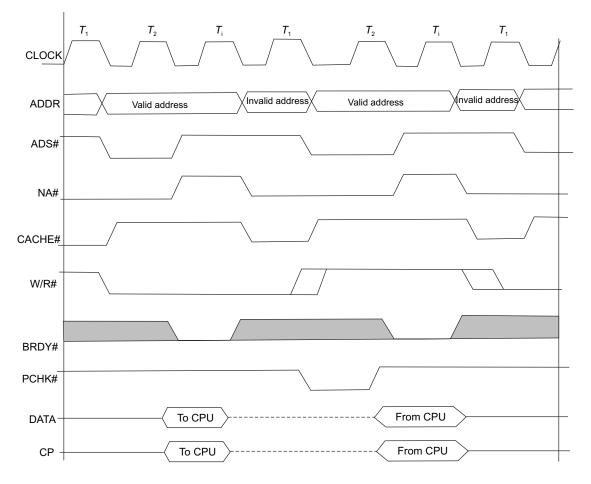

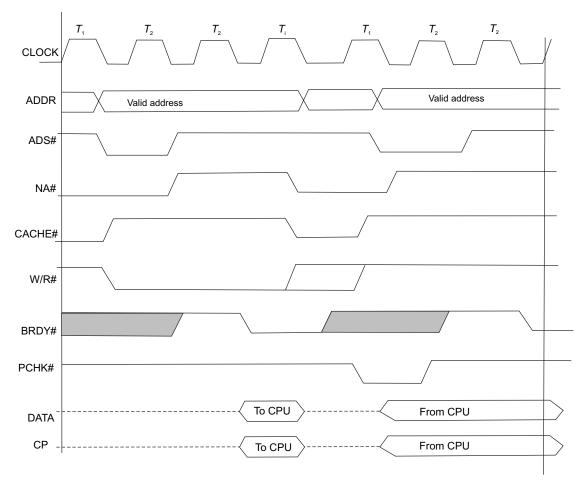

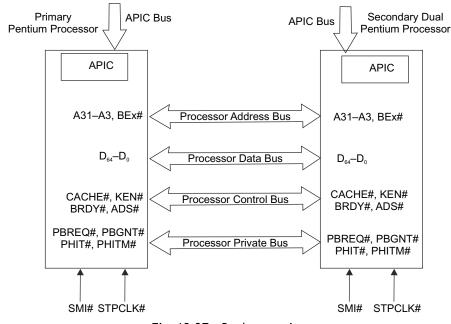

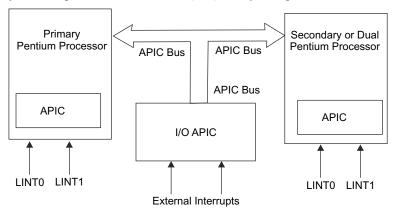

- 12.9 Pentium Bus Interfacing 677

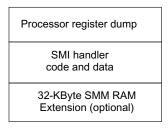

- 12.10 System Management Mode (SMM) of the Pentium Processor 684

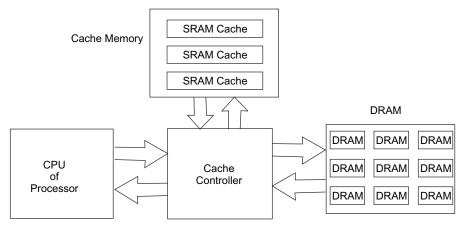

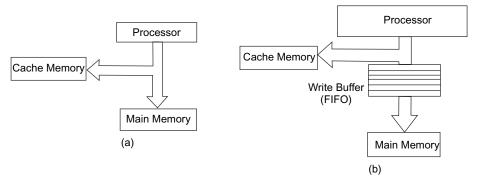

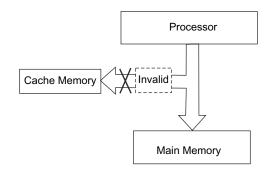

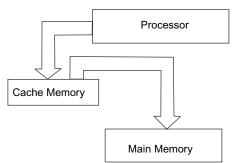

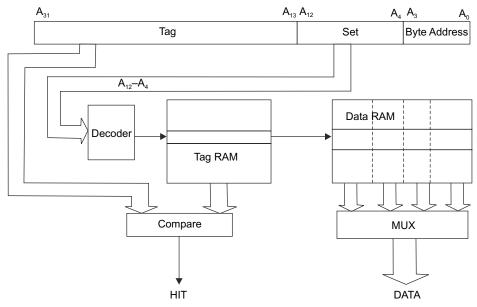

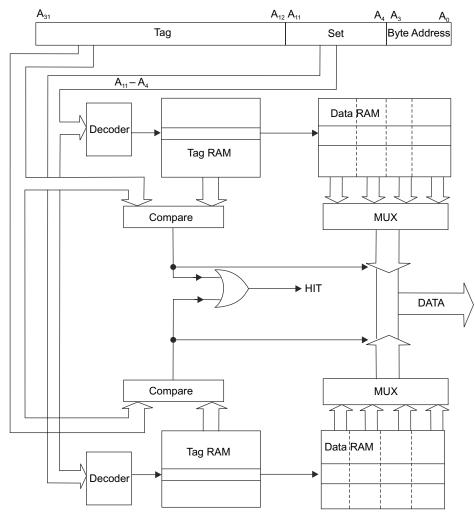

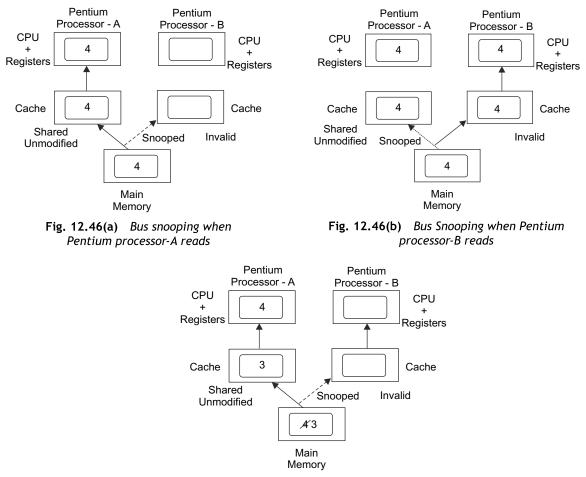

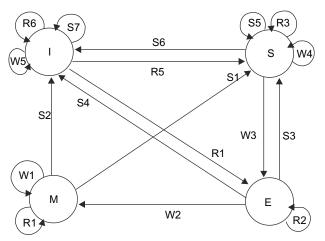

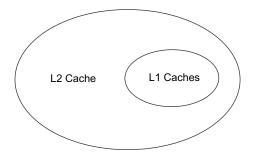

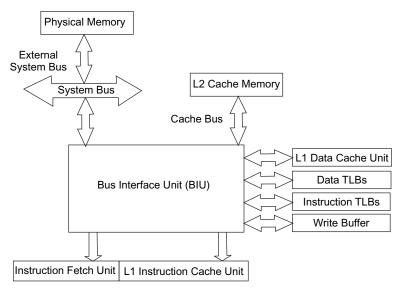

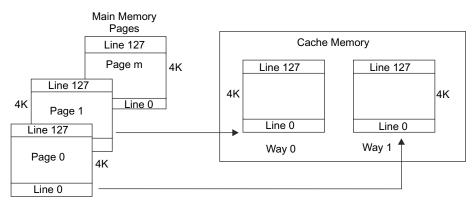

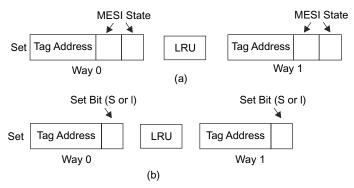

- 12.11 Cache Memories 686

- 12.12 Pentium MMX 697

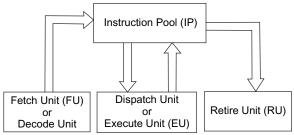

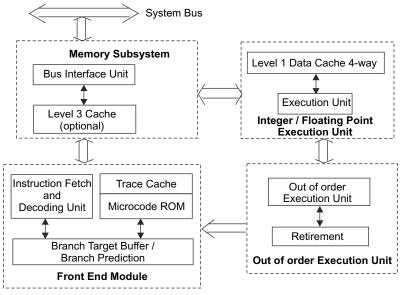

- 12.13 Pentium Pro, Pentium II, and Pentium III: P6 Family Processors 698

- 12.14 Comparison of Pentium and Pentium-Pro Processor 704

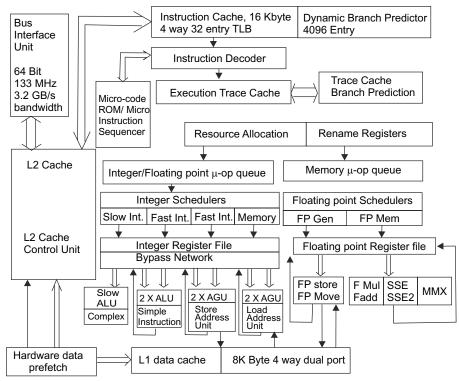

- 12.15 Pentium 4 Processor 705

- 12.15 Comparison of Pentium III and Pentium 4 Processors 713

- 12.16 Risc Processors 713

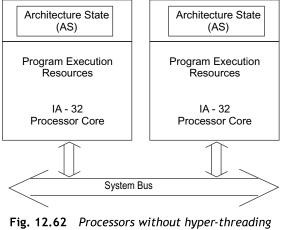

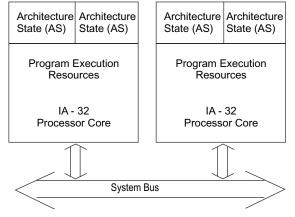

- 12.17 Core Processor 717

Summary 718

Multiple-Choice Questions 719 Short-Answer Questions 720 Review Questions 720 Answers to Multiple-Choice Questions 721

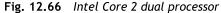

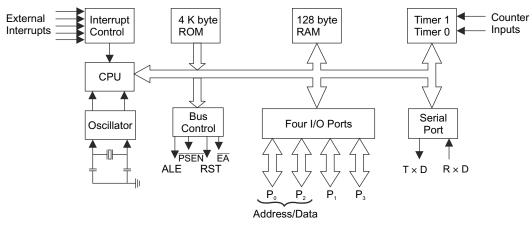

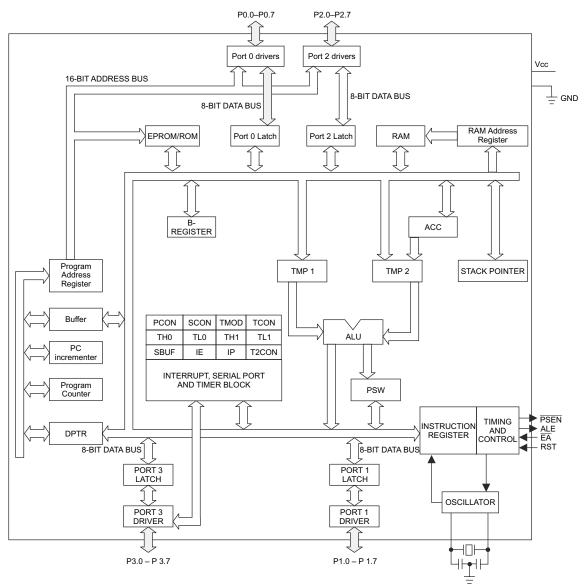

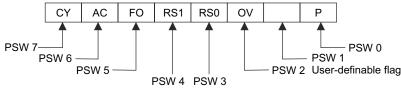

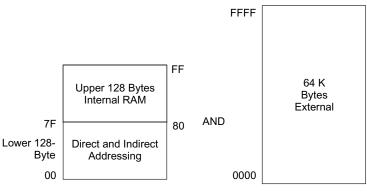

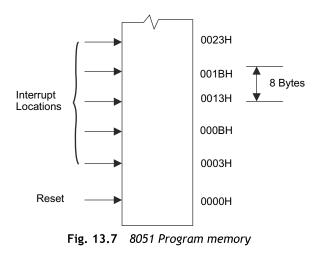

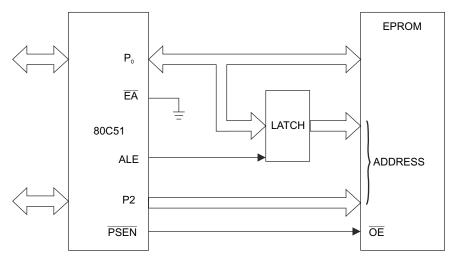

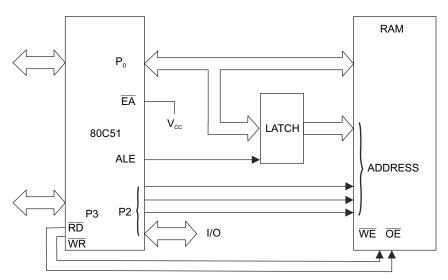

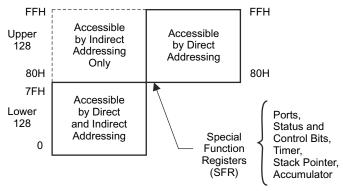

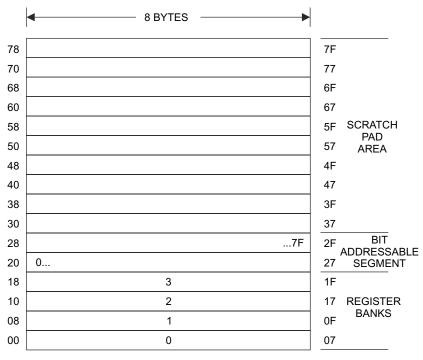

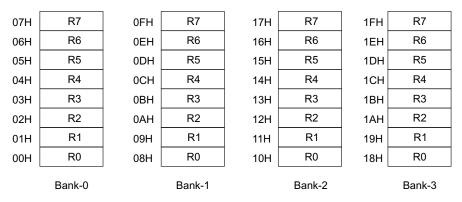

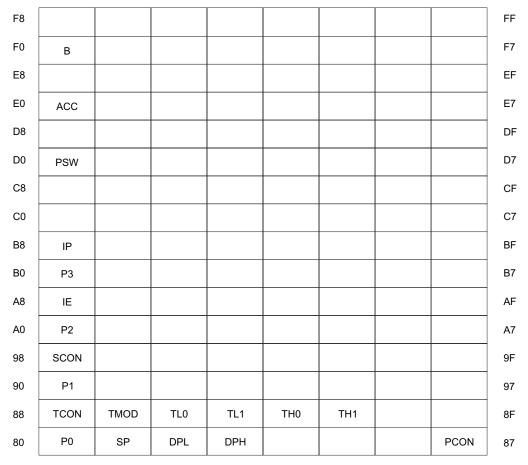

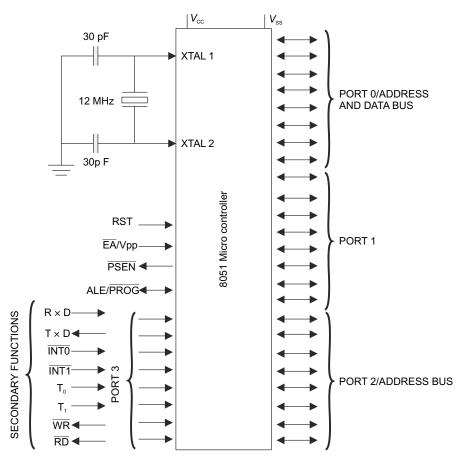

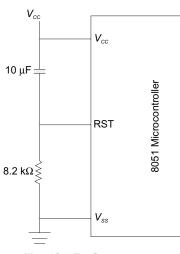

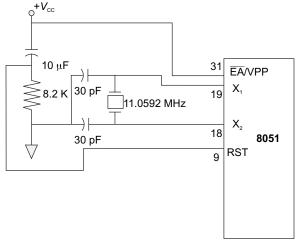

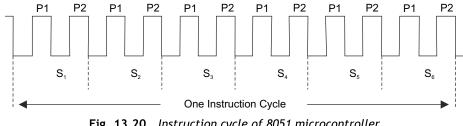

722 13.2 Architecture of 8051 Microcontroller 725

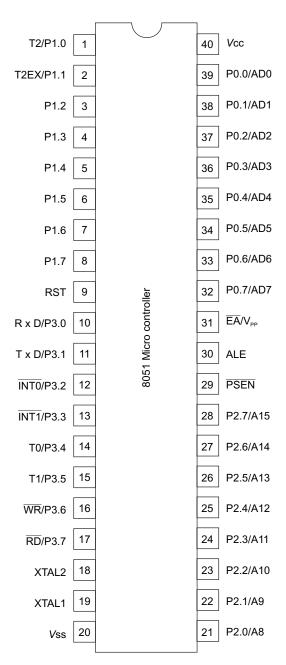

13.4 Pin Diagram of 8051 Microcontroller 735

#### 13. Introduction to 8051 Microcontroller

13.3 Memory Organization 730

13.5 Timers/Counters 744

Introduction

13.1

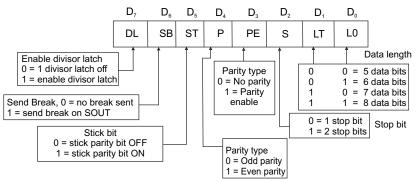

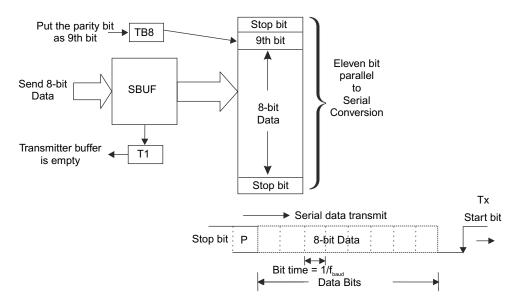

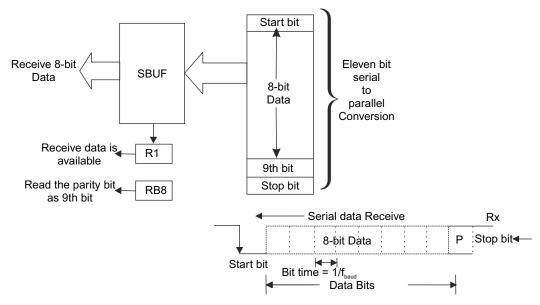

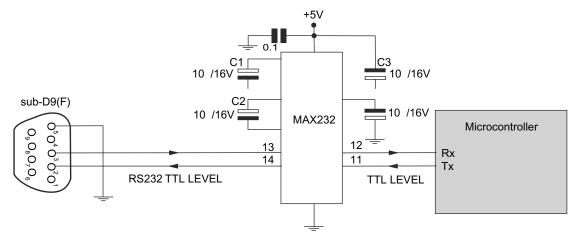

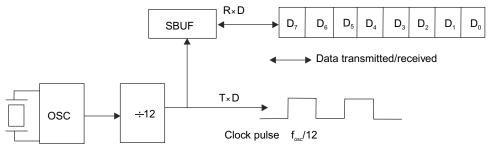

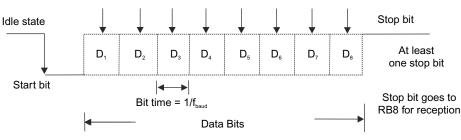

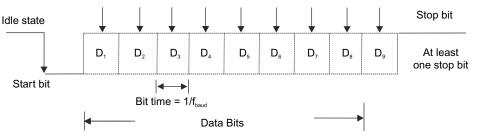

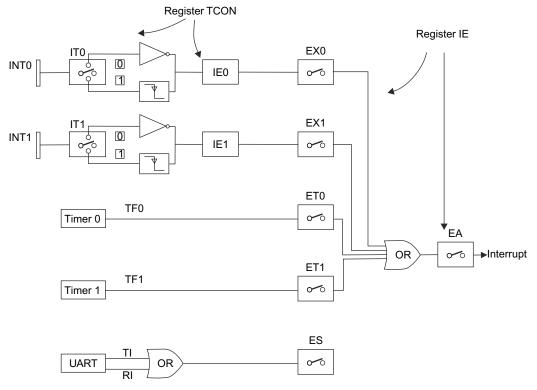

| 13.6 Serial Communication 749                                                  |     |

|--------------------------------------------------------------------------------|-----|

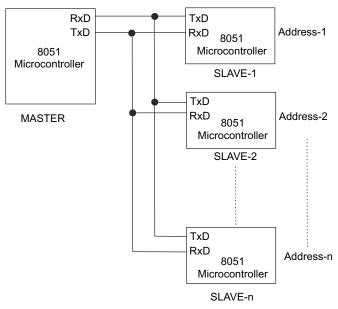

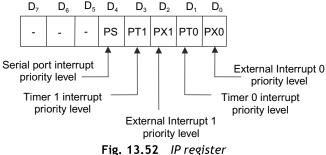

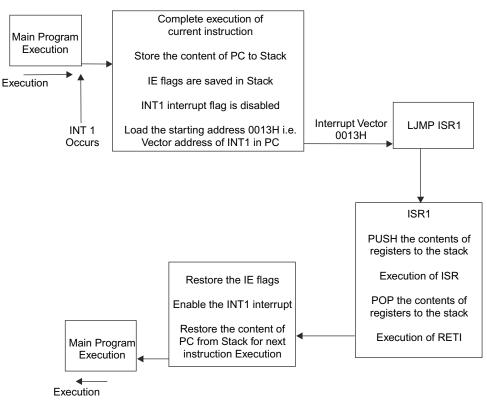

| 13.7 Interrupts 756                                                            |     |

| Summary 760                                                                    |     |

| Multiple-Choice Questions 760                                                  |     |

| Short-Answer Questions 761                                                     |     |

| Review Questions 761                                                           |     |

| Answers to Multiple-Choice Questions 762                                       |     |

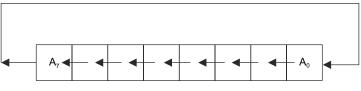

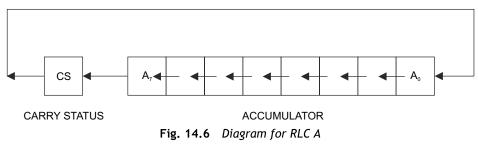

| 14. Instruction Set and Programming of the 8051 Microcontroller                | 763 |

| 14.1 Introduction 763                                                          |     |

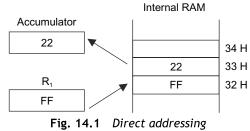

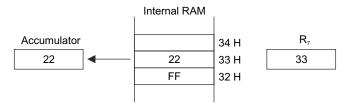

| 14.2 Addressing Modes 763                                                      |     |

| 14.3 8051 Instruction Set 767                                                  |     |

| 14.4 Simple Examples in Assembly-Language Programs of 8051 Microcontroller 792 |     |

| 14.5 Assembly-Language Programs 795                                            |     |

| 14.6 Applications of Microcontrollers 807                                      |     |

| Summary 827                                                                    |     |

| Multiple-Choice Questions 827                                                  |     |

| Short-Answer/Viva-Voce Questions 828                                           |     |

| Review Questions 828                                                           |     |

| Answers to Multiple-Choice Questions 829                                       |     |

| Appendix A - OPCODE of the 8085 Instruction Set                                | 830 |

| Appendix B - Some Important Tables for 8051                                    | 833 |

| Appendix C - Some Important Tables for 8085                                    | 838 |

| Appendix D - Some Important Tables for 8086                                    | 842 |

| Model Question Paper - 1                                                       | 856 |

| Model Question Paper - 2                                                       | 860 |

| Model Question Paper - 3                                                       | 863 |

| Index                                                                          | 867 |

Index

## PREFACE

#### Overview

Though progress and advancement in microprocessor technology has been very fast, the study of the basic principles, e.g. the digital building blocks of 8085 and 8086 microprocessors and 8051 microcontrollers are continuing. Nowadays, this subject forms a part of undergraduate courses, namely Electrical, Instrumentation, Electronics, Electronics and Communication, Computer Science and Engineering, and Information Technology. The present book, thus, aims to be of use to students of EE, CS & E, ECE, IN, IT and engineers working in automation industries.

#### Aim

Although a large number of books on microprocessors are available in the market, most cover either the 8085 microprocessor or its interfacing or advanced microprocessors like the 8086 to Pentium processors or the 8051 microcontroller. Consequently, there is no book that covers all the theory starting from the 8085 and 8086 microprocessors, 80186, 80286, 80386 and 80486 to Pentium processors and the 8051 microcontroller. Since almost none of the reference books have syllabus compatibility and right pedagogy, many students find it difficult to conceptualize the subject. As per feedback from students and teachers, there is need for a single book that can cover all the topics as per university curricula. This book is an outcome of my decade-long teaching experience of Microprocessors and Microcontrollers at SSGM College of Engineering, Shegaon; Panjab Engineering College, Chandigarh; and NITTTR, Kolkata. The content of this book covers the syllabi of microprocessors and microcontrollers of major Indian universities like WBUT, UPTU, PTU, RGTU, Mumbai University, Pune University, Anna University, JNTU, VTU, and many more.

I have written this book attempting to cover all the important topics of 8085 and 8086 microprocessors, 80186 to 80486 microprocessors, Pentium processors and the 8051 microcontroller. The examples of assembly-language programs and a variety of theoretical and multiple-choice questions at the end of each chapter give students a chance to check and enhance their conceptual understanding. Though this book is written to help students develop basic concepts of microprocessor and microcontroller architecture, programming and their applications, this course will also mitigate a definite percentage of every competitive examination of engineering professionals, namely IES, UPSC, GATE, etc.

#### Salient Features

Some salient features of this book are

- + Complete coverage of the syllabi on Microprocessors and Microcontrollers of major Indian universities

- + Large number of assembly-language programs incorporated from examination papers of different universities and competitive examinations like IES, UPSC, and GATE

- + Architecture, Programming, Interfacing of Microprocessors and Microcontrollers explained in lucid language

- + Detailed coverage of Advanced Microprocessors

- + Hands-on approach through applications such as Traffic Control, Keyboard Interfacing, Stepper Motor Control, Seven Segment Display, Control of Firing Circuit of a Thyristor

| xiv                                  | Preface                                                                                                             |                                                                                                                                                                                                                                 |  |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Feature                              | Description                                                                                                         | Benefit                                                                                                                                                                                                                         |  |  |

| <b>Brief Introduction</b>            | A brief description of the chapter topics is given.                                                                 | Student gets a subjective overview of the contents of the chapter.                                                                                                                                                              |  |  |

| Diagrams                             | Over 550 diagrams are given in the text.                                                                            | Diagrams are an important tool in<br>the presentation of text material in a<br>clear and lucid manner. These enable the<br>reader to effectively understand the vari-<br>ous microprocessor concepts discussed<br>in a chapter. |  |  |

| Definitions                          | Wherever appropriate, useful definitions related to the topic being described have been inserted.                   | These will help the students to quickly revise the definitions before an exam.                                                                                                                                                  |  |  |

| Solved Examples/<br>Programs         | Close to 100 Solved Examples/<br>Programs are present in the text.                                                  | A stepwise approach for solving prob-<br>lems is used throughout the book,<br>thereby making it easier for the reader to<br>apply the learnt concepts.                                                                          |  |  |

| Summary                              | A concise Summary is provided at the end of each chapter.                                                           | It underlines the important concepts learnt in the chapter.                                                                                                                                                                     |  |  |

| Multiple-Choice<br>Questions         | More than 250 Multiple-Choice<br>Questions are present in the text.                                                 | These help readers have a quick revision of the concepts discussed in the chapter.                                                                                                                                              |  |  |

| Review Questions                     | Almost 400 Review Questions<br>are given in the text to test the<br>theoretical grasp of the students.              | These are set to develop confidence in<br>the principles discussed and check the<br>understanding of the student.                                                                                                               |  |  |

| Short-Answer/<br>Viva-Voce Questions | 130 Short-Answer/Viva-Voce<br>Questions are present as<br>chapter-end pedagogy.                                     | These will be helpful in revising the concepts and preparing for competitive exams.                                                                                                                                             |  |  |

| Model Question Papers                | 3 Model Question Papers are<br>provided at the end of the text<br>which focus on university<br>patterned questions. | Essentially, these Model Question<br>Papers make the reader realize the<br>pattern of questions in university<br>examinations.                                                                                                  |  |  |

### **Chapter Organization**

This book has 14 chapters. Chapter 1 covers the evolution of microprocessors and their applications in detail. Chapters 2 to 4 are devoted to the 8085 microprocessor architecture, addressing modes, instruction set and assembly-language programs; whereas chapters 5 to 7 cover architecture of 8086 and 8088 microprocessors, addressing modes, instruction set, assembly-language programs and 8087, 80287 and 80387 numeric data processors. Chapters 8 and 9 incorporate the interfacing devices of 8085 and 8086 microprocessors. Chapter 10 deals with the applications of 8085 and 8086 microprocessors. Chapters 11 and 12 cover advanced microprocessors. Finally, chapters 13 and 14 discuss the architecture, addressing modes, instruction set, assembly-language programs and applications of 8051 microcontroller.

Given below is a detailed chapter synopsis.

**Chapter 1** presents the basic concept of microprocessors and microcontrollers, history of microprocessors, evolution of microprocessors and its applications, evolution of microcontrollers and their applications.

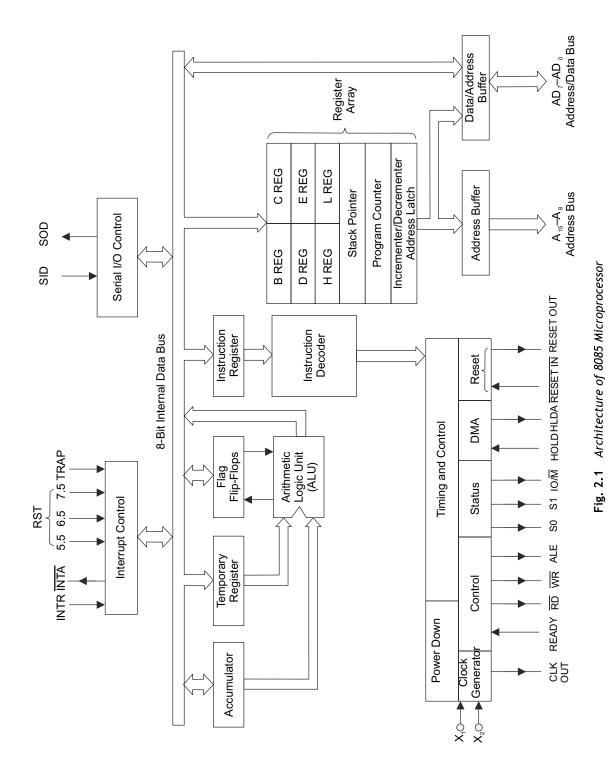

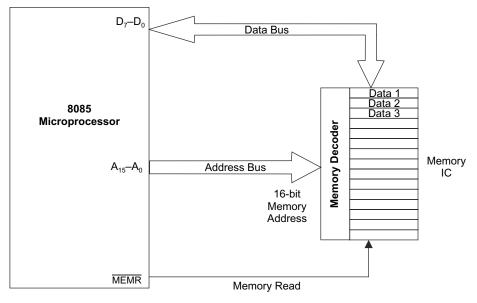

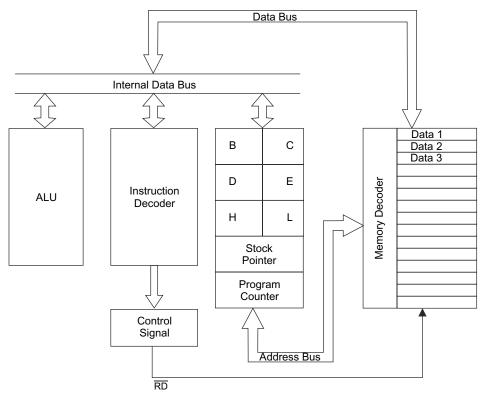

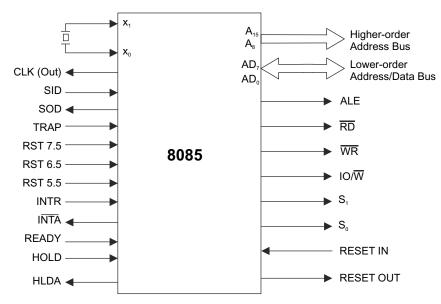

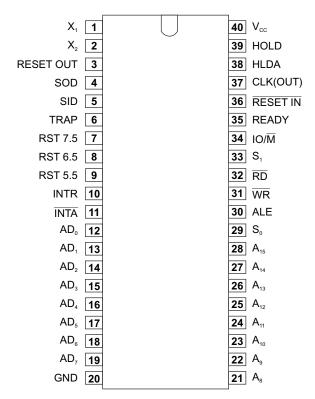

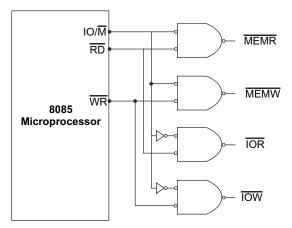

**Chapter 2** deals with the architecture of the 8085 microprocessor in a generalized way. This chapter covers the block diagram of the 8085 microprocessor and its operating principles. It also elaborately explains the pin diagrams of 8085 microprocessors and functions of pins.

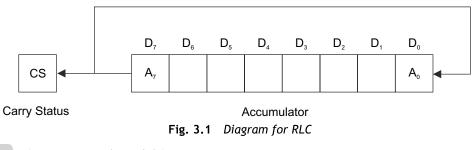

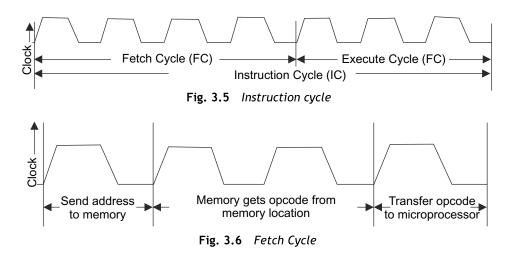

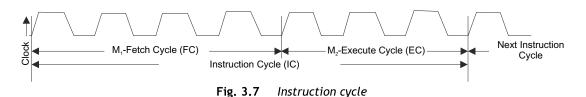

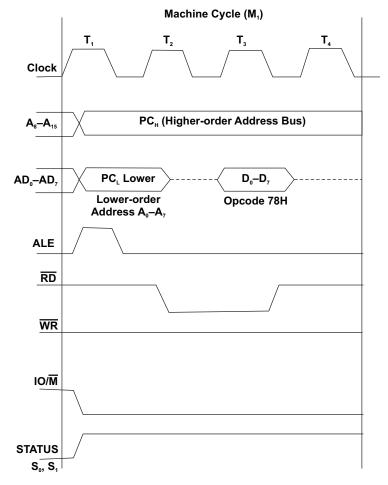

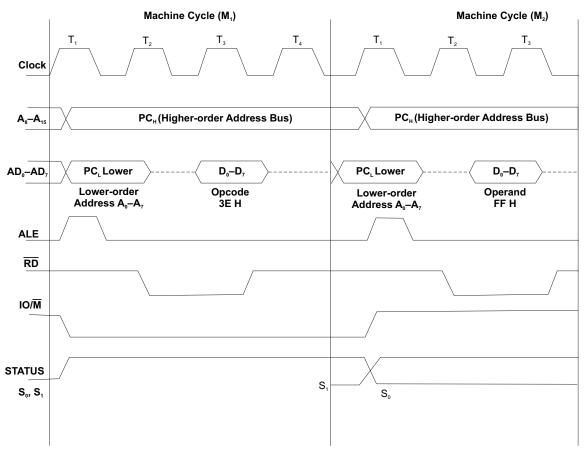

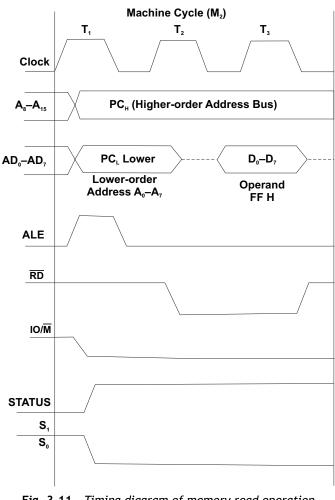

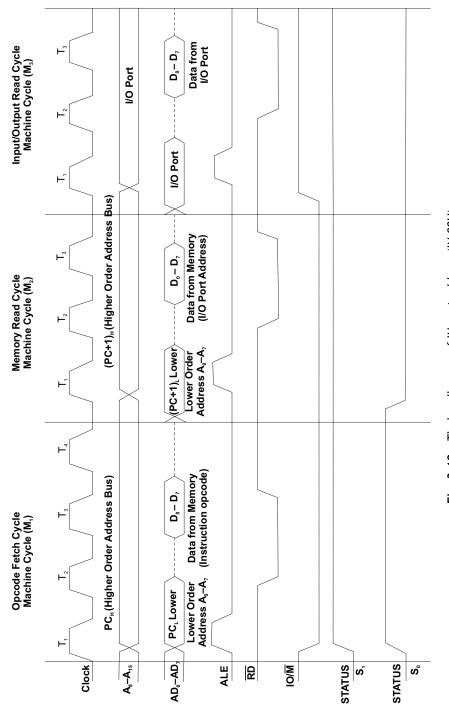

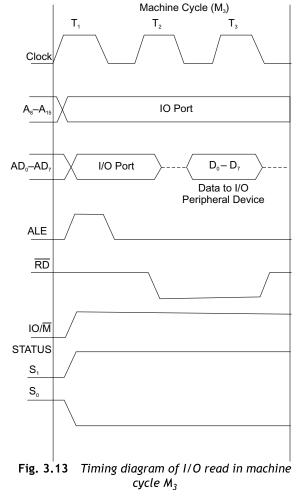

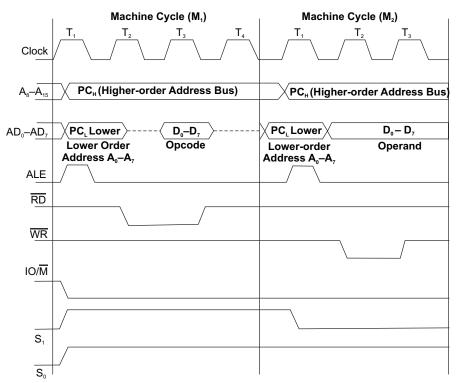

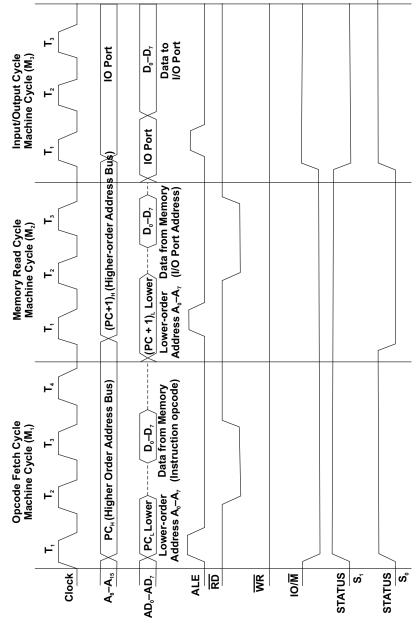

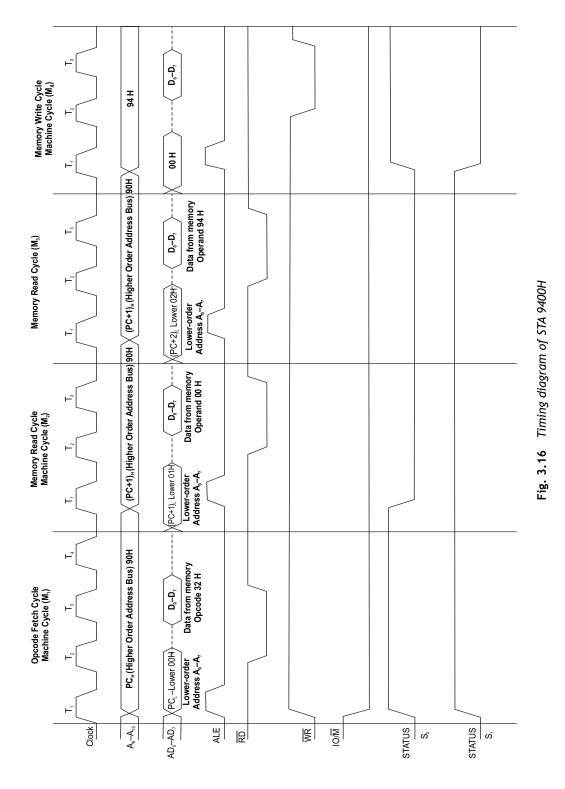

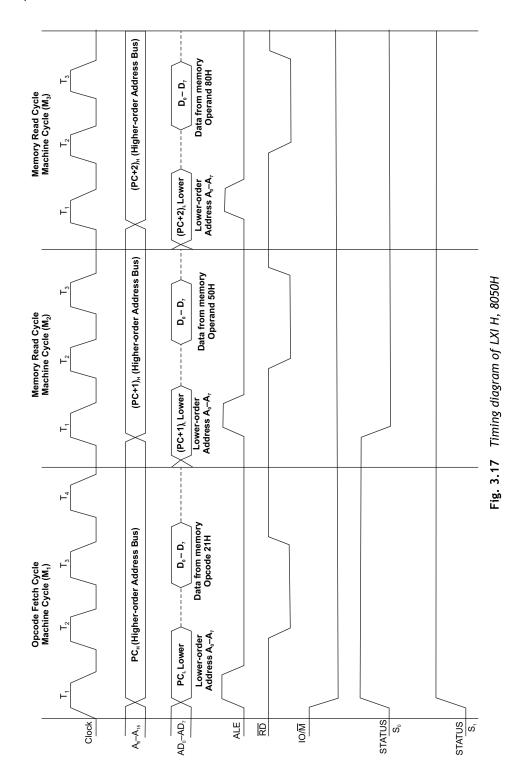

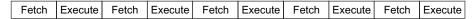

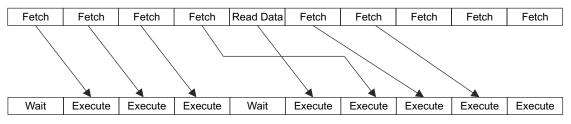

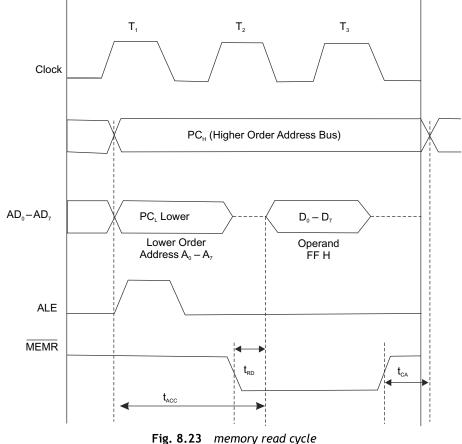

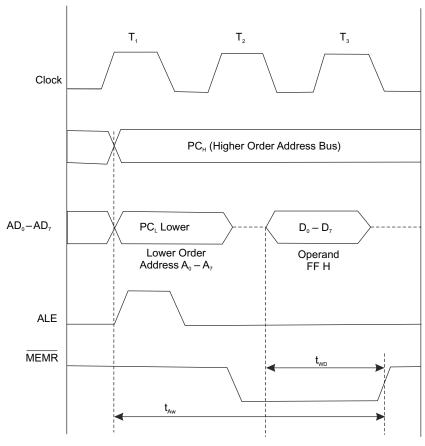

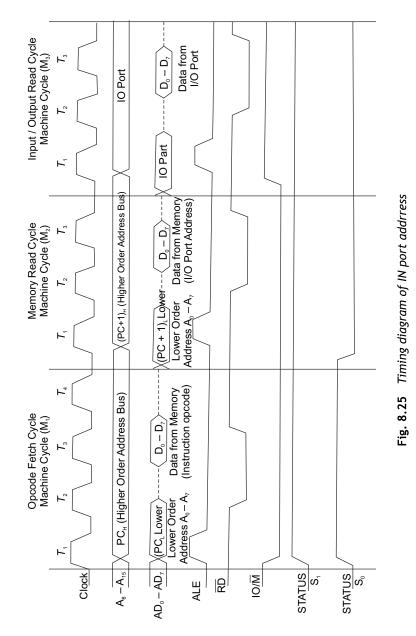

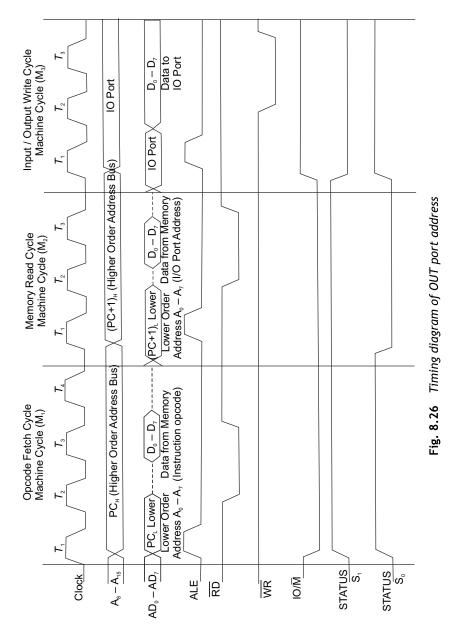

**Chapter 3** describes the different addressing modes and instruction sets of the 8085 microprocessor. There is detailed discussion on instruction timing diagrams of  $8085\mu$ P, fetch cycle, execute cycle and machine cycles, timing diagram of memory read, memory write, I/O read and write operations.

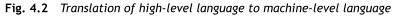

**Chapter 4** deals with machine-level languages, assembly-level languages, and high-level languages with detailed coverage of operation of stacks, subroutines and time delay loops. This chapter also incorporates modular programming, macro, instruction formats and assembly-language programs.

**Chapter 5** introduces the architecture of 8086 and 8088 microprocessors. It also covers minimum-mode and maximum-mode configurations, memory addressing, pin descriptions of 8086 and 8088, and other supporting ICs such as 8284A, 8286/8287, 8282/8283 and 8288.

Chapter 6 covers the different addressing modes and instruction set of the 8086 in detail.

**Chapter 7** introduces assembly-language commands and assembly-language programs of 8086. This chapter also includes the architecture of the 8087 numeric data processor, pin descriptions, interfacing with 8086, instruction set and assembly-language programs of 8087 with explanation on the architectures of numeric data processors 80287 and 80387.

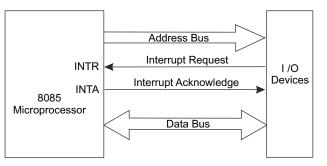

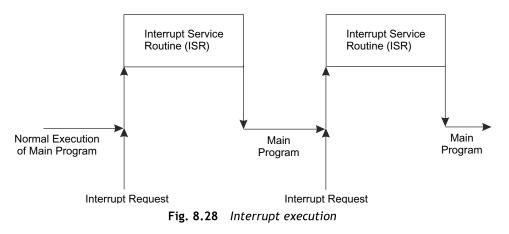

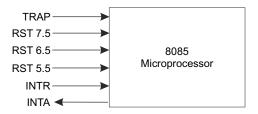

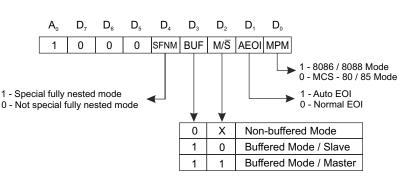

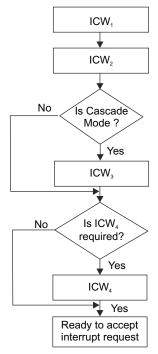

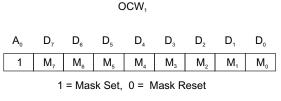

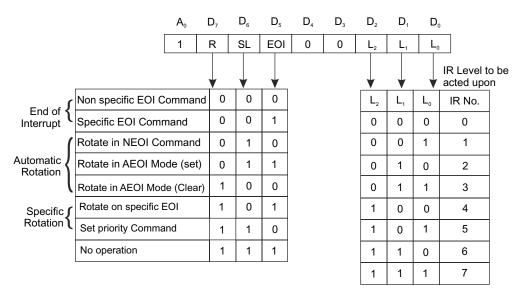

Programmable peripheral chips are equipment that support any interfacing devices with microprocessors. There are many such devices available in the market. **Chapter 8** covers memory ICs and their interfacing, interrupts of 8085, 8086 and 8088 microprocessors, 8259 Programmable Interrupt Controller, 8255A Programmable Peripheral Interface, and the 8253 Programmable timer/counters.

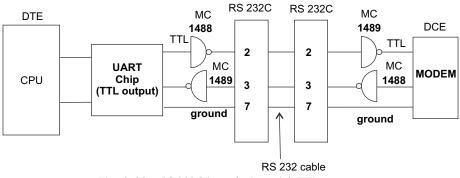

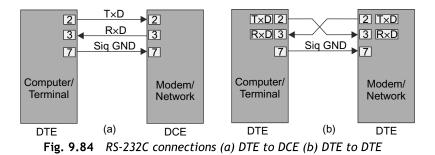

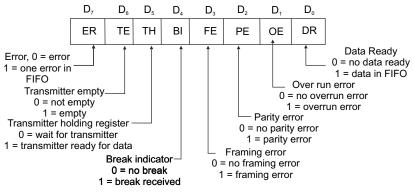

**Chapter 9** presents the 8251 Serial Communication Interface, 8279 Programmable Keyboard and Display Interface, 8257 Direct Memory Access (DMA) Controller, 8275 CRT controller, ADC as well as DAC ICs and their interfacing, Bus interface, RS232C, IEEE-488, Parallel printer interface, 8250 UART, 16550 UART and 8089 I/O processor.

In industries, there are varieties of microprocessor applications such as instrumentation, industrial automation and aerospace, etc. The applications of microprocessors in display systems; measurement of electrical quantities such as voltage, current, frequency and phase angle; measurement physical quantities like displacement, strain, force, temperature, water level and speed; microprocessor-based protection, traffic light control, and speed control of motors are incorporated in **Chapter 10**.

**Chapter 11** describes the 80186 microprocessor architecture, pin description, addressing modes, data types and instruction sets. It also covers the architecture, pin description, addressing modes (real addressing modes and protected virtual address mode), data types and instruction sets of the 80286 microprocessor, and the operations of 808386 and 80486.

Chapter 12 presents Pentium architecture, Pentium operating modes, segmentation, physical, linear and logical address, virtual 8086 mode, pin descriptions of Pentium processors, cache memories, Pentium MMX processor, Pentium Pro, Pentium II, Pentium III and Pentium 4 processors, RISC and CISC processors in detail.

**Chapter 13** describes the architecture of the 8051 microcontroller. This chapter also describes the special function registers and memory organization, timer/counters, interrupts and serial communication of the 8051 microcontroller.

| xvi | Preface |  |

|-----|---------|--|

|     |         |  |

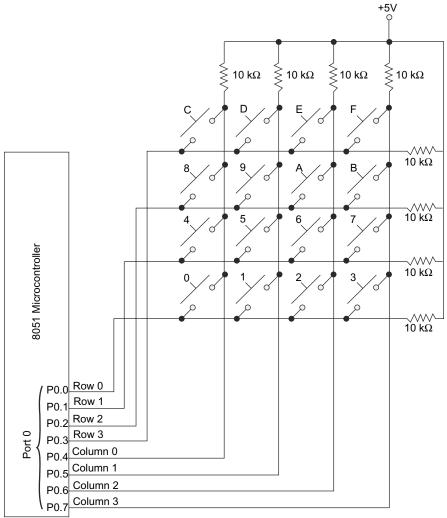

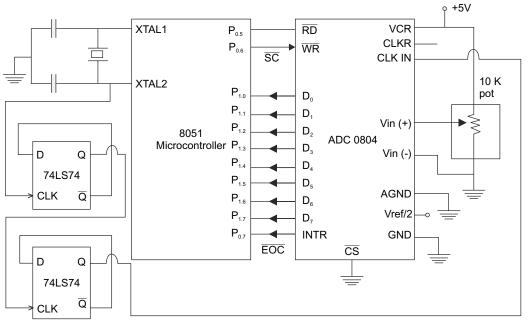

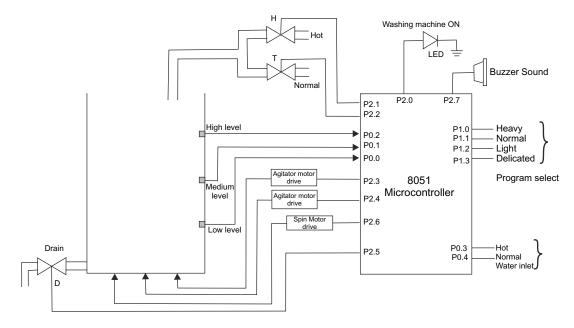

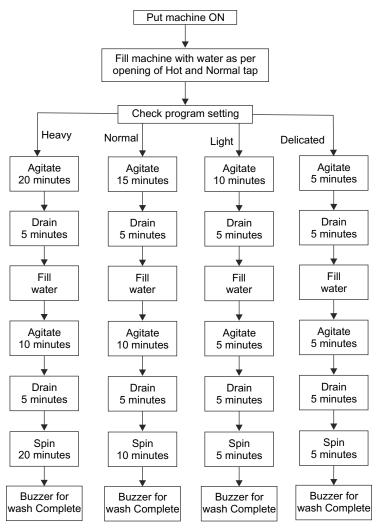

**Chapter 14** deals with the addressing modes and instruction set of the 8051 microcontroller with elaborate emphasis on assembly-language programs for the 8051 microcontroller, and applications of microcontrollers for keyboard interfacing, A/D converter interfacing, traffic light control, stepper motor control and washing machine control.

Appendix A covers opcodes of the 8085 instruction set.

Appendix B provides the instruction-set summary for 8051.

Appendix C contains the instruction-set summary for 8085

Appendix D includes the instruction-set summary for 8086.

Finally, there are Model Question Papers at the end of the book.

#### **Web Supplements**

This book also has an exhaustive Online Learning Centre, which can be accessed at <u>https://www.mhhe.com/</u><u>mandal/</u> designed to provide valuable resources for instructors and students.

- + For Instructors

- Powerpoint Slides (chapter-wise)

- Solution Manual For Selected Questions

- Tutorial Sheets

- + For Students

- Instruction Set of 8085 Microprocessor

- Instruction Set of 8086 Microprocessor

- Instruction Set of 8051 Microcontroller

- Lab Experiments Manual

- Answers for selected Review Questions

- Viva-voce Questions with Answers

- References/Suggested Further Reading

#### Acknowledgements

I have received cooperation and inspiration for this book from Dr Gurnam Singh, PEC, Chandigrah; Dr S Chatterjee, NITTTR, Chandigarh; Dr S K Bhattachariya, Former Director, NITTTR, Kolkata; Prof. Amitabha Sinha, Director School of IT, WBUT; Dr C K Chanda and Dr P Shyam, Bengal Engineering College, Shibpur; Dr P Sarkar, Professor and Head Electrical, Dr S Chattopadhay, Associate Professor, and Dr S Pal, Asst. Professor, NITTTR, Kolkata. I am also thankful to other staff of Electrical Engineering—Mr A K Das, Mr N K Sarkar, Mr S Roy Choudhury and Mr Surojit Mallick—who helped me complete the manuscript of this book.

At this juncture, I would also like to express my gratitude to the numerous reviewers who took out time to review the manuscript. Their names are given below.

| Madan Mohan Agarwal | Birla Institute of Technology, Jaipur, Rajasthan                                            |

|---------------------|---------------------------------------------------------------------------------------------|

| P K Mukherjee       | Institute of Technology—Banaras Hindu University (IT—BHU), Varanasi, Uttar Pradesh          |

| Siddharth Chauhan   | National Institute of Technology (NIT), Hamirpur, Himachal Pradesh                          |

| Vishal Nimbork      | Ajay Kumar Garg College of Engineering, Ghaziabad, Uttar Pradesh                            |

| Sampath Kumar V     | Jagadguru Sri Shivarathreeshwara (JSS) Academy of Technical Education, Noida, Uttar Pradesh |

|                          | Preface                                                                        | xvii |

|--------------------------|--------------------------------------------------------------------------------|------|

| Agamani Chakraborty      | Asansol Engineering College, Asansol, West Bengal                              |      |

| Pinaki Ranjan Ghosh      | ADAMAS Institute of Technology, Kolkata, West Bengal                           |      |

| Jaydip Nath              | Future Institute of Engineering and Management (FIEM), Kolkata,<br>West Bengal |      |

| A G Keskar               | Visvesvaraya National Institute of Technology, Nagpur, Maharashtra             |      |

| C A Ghuge                | PE Society's Modern College of Engineering, Pune, Maharashtra                  |      |

| Sunil N Kore             | Walchand College of Engineering, Sangli, Maharashtra                           |      |

| Vikas J Dongre           | Government Polytechnic, Nagpur, Maharashtra                                    |      |

| Lyla B Das               | National Institute of Technology (NIT), Calicut, Kerala                        |      |

| S Solai Manohar          | College of Engineering, Anna University, Chennai, Tamil Nadu                   |      |

| Jayakumar Vijayaraghavan | Rajalakshmi Engineering College, Chennai, Tamil Nadu                           |      |

| S R Malathi              | Sri Venkateshwara College of Engineering, Chennai, Tamil Nadu                  |      |

| S Rathinavel             | Sri Subramanya College of Engineering and Technology, Udumalpet,<br>Tamil Nadu |      |

| M Sreelatha              | Kakatiya Institute of Technology and Science, Warangal, Andhra Prade           | sh   |

| M Shailaja               | JNTU College of Engineering, Kakinada, Andhra Pradesh                          |      |

| M Sampath Kumar          | College of Engineering, (Andhra University), Visakhapatnam,<br>Andhra Pradesh  |      |

#### Feedback

Any suggestions for improving the contents of the text are always welcome. Please give suggestions or feedback to the publisher's email id mentioned below.

#### Soumitra Kumar Mandal

#### **Publisher's Note**

Do you have a feature request? A suggestion? We are always open to new ideas (the best ideas come from you!). You may send your comments to tmh.csefeedback@gmail.com (kindly mention the title and author name in the subject line).

Piracy-related issues may also be reported.

## Chapter 1

# Introduction to Microprocessors and Microcontrollers

## 1.1 INTRODUCTION

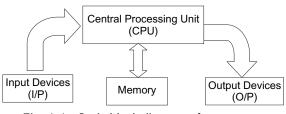

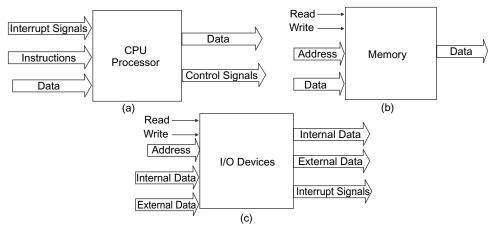

The computer is a machine that processes data to generate information with speed and accuracy. Electronic and electromechanical devices, and software make this programmable machine The basic block diagram of a computer is shown in Fig. 1.1. The computer comprises four basic units, namely, input (I/P), memory, output (O/P), and central processing unit.

#### 1.1.1 Input Devices

An input device accepts data from the environment, converts it into digital form and sends it to the memory of the computer for storing. Commonly used input devices are punched cards, paper tapes, magnetic tapes, floppy disks, and magnetic disks.

used input devices are punched cards, paper tapes, magnetic tapes, floppy disks, and magnetic disks. Card readers, paper tape readers, magnetic tape readers, disk drives read data transmitted by input devices. A keyboard terminal can be used as input to the computer. Optical mark readers and optical character readers, are input devices that are scanned by an array of photocells. The input is then converted into machine code and transmitted into the memory of the computer for processing. On identical principles, bar-code readers read the information prepared in bar code for application by computers. In magnetic ink readers, information

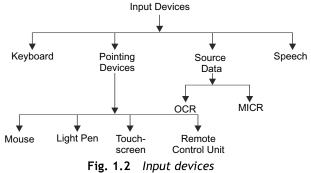

written or printed in magnetic ink is read and transmitted directly to the memory for processing. Electronic mouse, touchscreens, and light pens are also used Input Devices as input devices. Figure 1.2 shows the different input devices.

#### 1.1.2 Memory

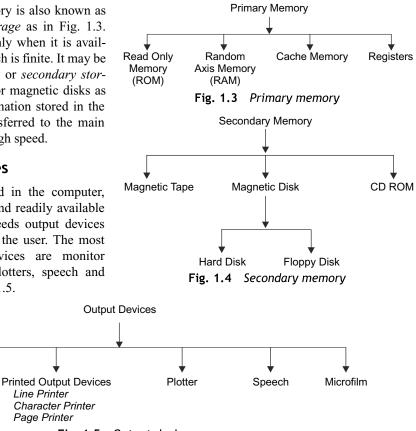

A computer system also has storage areas, often referred to as memory. The memory unit stores the information to be processed by the CPU. This information consists of the program as well as data. The memory can receive data, hold them and deliver them when instructed to do so. The

#### 2 Microprocessors and Microcontrollers

storage available in the memory is also known as *main storage* or *primary storage* as in Fig. 1.3. The data can be processed only when it is available in the main memory, which is finite. It may be increased by adding auxiliary or *secondary storage*, such as magnetic tapes or magnetic disks as shown in Fig. 1.4. The information stored in the auxiliary storage can be transferred to the main memory for processing at a high speed.

#### 1.1.3 Output Devices

**Display Devices**

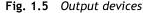

Monitor

When a program is executed in the computer, the result will be computed and readily available for display. The computer needs output devices to display the information to the user. The most commonly used output devices are monitor screens, printers, graphics plotters, speech and microfilm as depicted in Fig. 1.5.

#### 1.1.4 Central Processing Unit

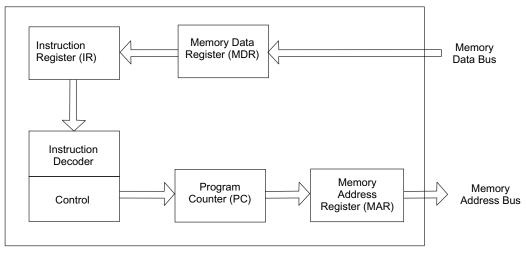

The central processing unit is the brain of the computer. It executes the programmer's software and controls the memory, input and output devices. Programs are stored in the memory. The CPU fetches instructions

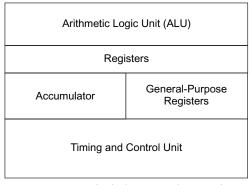

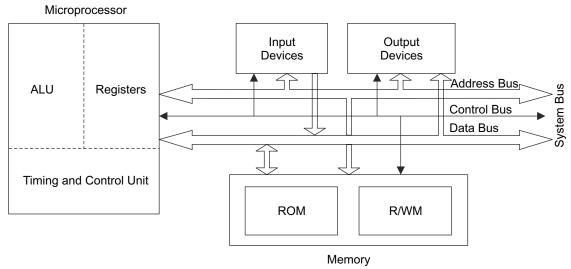

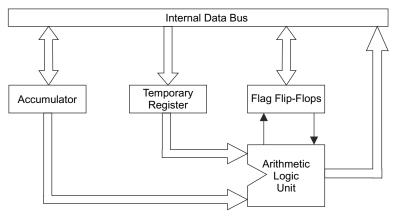

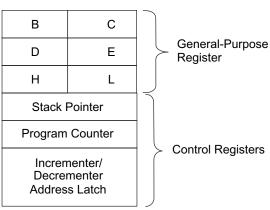

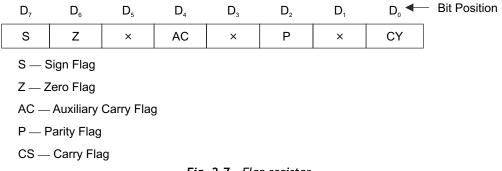

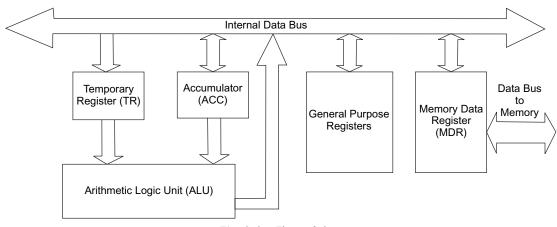

of a program sequentially from the memory. It fetches one instruction at a time, decodes it and then executes it. After decoding an instruction, the CPU comes to know what operations are to be performed. It also comes to know whether the data to be processed are in the memory, general-purpose registers of the microprocessor or at input/output ports. If data are in the general-purpose registers, the CPU executes the program. The CPU controls memory, input and output devices to receive, store and send data/result of the program under execution. Under its control programs, data and results are displayed on the CRT, stored in the memory or printed by the printer. The major components of a CPU are ALU, timing and control unit and registers as depicted in Fig. 1.6.

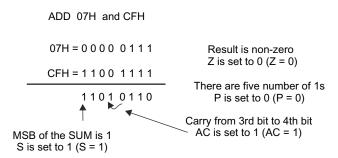

**Arithmetic Logic Unit (ALU)** The ALU performs the actual processing of data including addition, subtraction, multiplication and also division. This unit also performs certain logical operations such as comparing two numbers to see if one is larger than the other or if they are equal. Arithmetic or logic operations are performed by bringing the required operands into the ALU. Suppose two numbers located in the main memory are to be added. They are brought into the arithmetic unit and temporarily stored in registers or in accumulators associated with this unit where the actual addition is carried out. The result is placed in one of the registers and subsequently transferred to the memory.

**Control Unit** The control unit directs and coordinates all activities of the computer system including the following:

- + Control of input and output devices

- + Entry and retrieval of information from storage

- + Routing of information between storage and arithmetic logic unit

- + Direction of arithmetic and logical operations

Although the control section does not process data, it acts as a central nervous system for the other data manipulating components of the computer. At the beginning of the processing, the first program instruction is selected and fed into the control section from the program storage area. Thus it is interpreted, and from there signals are sent to other components to execute the necessary action.

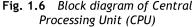

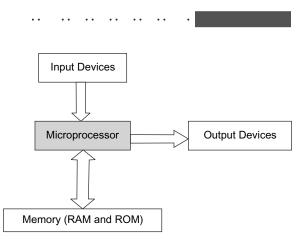

The central processing unit built on a single IC is called a *microprocessor*. In a microcomputer, the microprocessor acts as the central processing unit. Figure 1.7 shows the block diagram of microcomputer. Architecture of microprocessors is explained in this chapter.

Fig. 1.7 Basic block diagram of a microcomputer

## **1.2** MICROPROCESSOR

The microprocessor is a multipurpose, programmable, and clock-driven integrated circuit. This IC can read binary instructions from any storage device called memory. It also accepts binary data as input, processes data according to instructions, and provides results as output.

The microprocessor is the Central Processing Unit (CPU) of digital computers and it is constructed with IC technology. Figure 1.8 shows the block diagram of a microprocessor. The microprocessor has a digital circuit for data handling and computation under program control. The microprocessor is a data-processing unit. Data processing includes both computation and data handling. Computation is performed by logic circuits called the Arithmetic Logic Unit (ALU). The ALU is used to perform Add, Subtract, AND, OR, XOR, Compare, Increment, and Decrement functions. The ALU cannot perform any functions without control signals. In order to process data, the microprocessor must have control logic which instructs the microprocessor how to decode and execute the program. A program is a set of instructions required by a computer to perform any task.

#### 4 Microprocessors and Microcontrollers

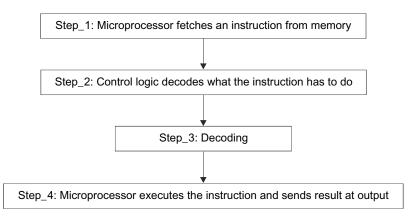

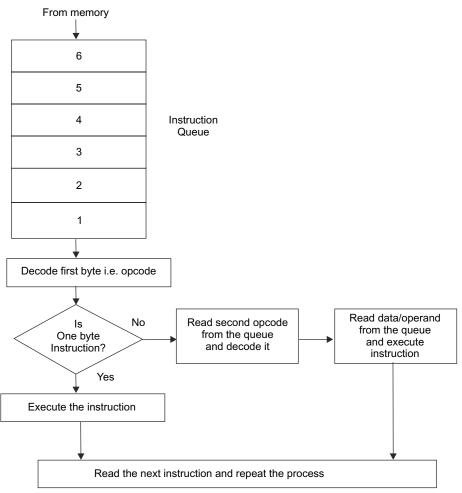

The control logic sends signals to the microprocessor and instructs how to operate the stored instructions in memory. Figure 1.9 shows the operation technique of a microprocessor. There are four steps of operation. In Step 1, the microprocessor fetches an instruction and in the next step, the control logic decodes what the instruction has to do. Then decoding is done in the third step and in the last step, the microprocessor executes the instruction.

The microprocessor always operates in binary digits 0 and 1, known as bits. Bit is an abbreviation for 'binary digit' which can be represented in terms of voltages. The microprocessor recognizes and processes a group of bits called *word*. Microprocessors are classified according to their word length such as 8-bit, 16-bit, 32-bit and 64-bit microprocessors. Microprocessor ICs are programmable so that instructions can be executed by a microprocessor to perform given tasks within its capability. The instructions are stored in a storage device which is called the memory, and the microprocessor can read instructions from the memory.

Fig. 1.9 Operation technique of a microprocessor

## **1.3** MICROCOMPUTER

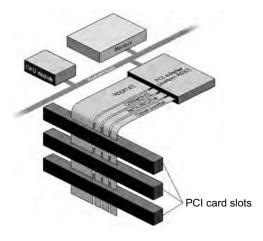

Generally, the words 'microprocessor' and 'microcomputer' are used to correspond to the same thing, but in fact these words have different meanings. The microprocessor is an Integrated Circuit (IC) developed on LSI or VLSI technology. It is the core of any computer system, but a microprocessor by itself is completely useless, until external peripheral devices are connected with it to enable it to interact with the outside world. The microcomputer is a complete computing system and it is built with a microprocessor, input/output devices and memory (RAM and ROM). The schematic block diagram of a microcomputer is shown in Fig. 1.10. The detailed architecture of a microcomputer is illustrated in Fig. 1.11.

Fig. 1.10 Schematic block diagram of a microcomputer

Fig. 1.11 Architecture of a microcomputer

**Arithmetic/Logic Unit (ALU)** The ALU performs arithmetic operations such as addition, subtraction, multiplication and division, and logic operations, namely, AND, OR, XOR, Complement, Rotate and Shift. After the operations, results must be stored either in a specified register or in the memory.

**Register** The microprocessor has various general-purpose registers such as B, C, D, E, H, L, and the Accumulator (A). These registers are used to store data and addresses temporarily during the execution of a program.

**Timing and Control Unit** The timing and control unit provides the necessary timing and control signals to perform any operation in the microcomputer. Actually, it controls the flow of data between the microprocessor and memory/peripheral devices.

*Input Devices* The input devices transfer data in binary from the outside world to the microprocessor. The most commonly used input devices are the keyboard, switches, mouse, scanner, and analog-to-digital converter.

**Output Devices** The output devices transfer data from the microprocessor to the outside world, e.g, printers, plotters, monitors, and magnetic tapes.

**Memory** The memory unit stores the binary information such as instructions and data, and provides that information to the microprocessor for processing. To execute any instruction, the microprocessor reads instructions and data from memory. After the computational operations in the ALU, microprocessor again stores results in memory for further use.

#### 6 Microprocessors and Microcontrollers

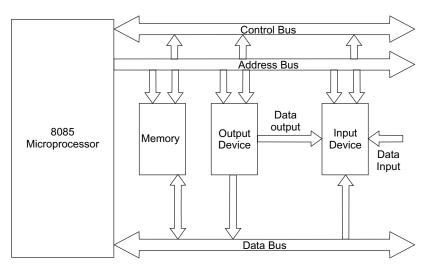

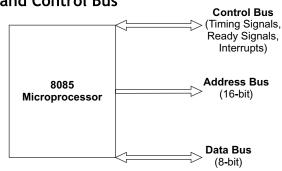

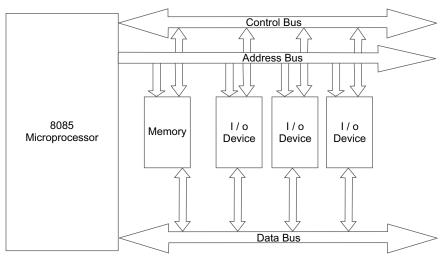

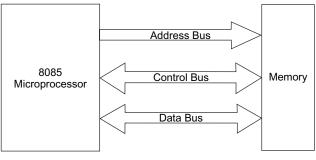

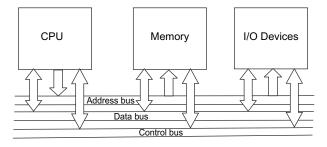

**System Bus: Address Bus, Data Bus and Control Bus** The microprocessor always communicates with input/output devices and memory via some path called the *system bus*. The system bus consists of address bus, data bus and control bus. *Address bus* is used to locate any input/output devices and memory. *Data bus* is used to transfer data in binary form between the microprocessor and peripherals. The microprocessor communicates with only one peripheral at a time. The timing signals are provided by the control bus of the microprocessor.

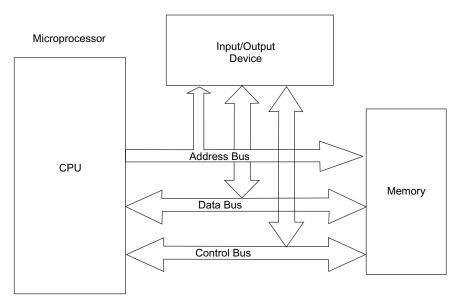

## **1.4** ARCHITECTURE OF MICROPROCESSORS

Usually, the function of microprocessors is to process or manipulate data. Except data manipulations, the processor is used to read data and instructions from the memory, read and write data to the memory, read data from input devices and write data into output devices. To perform these operations, the processor communicates with the memory and I/O devices through the address bus, data bus and control bus.

The *address bus* carries the address information from the processor to locate the memory as well as I/O devices. This bus is unidirectional.

The data bus carries the data between the processor and peripheral devices. This bus is bi-directional.

The *control bus* is used to carry control/status information. This bus is bi-directional. Figure 1.12 shows the interaction between processors and memory and I/O devices using address bus, data bus and control bus.

Fig. 1.12 Communication between CPU and memory and input/output devices

Depending upon the number of data buses and memory, there are three types of processor architecture such as

- (i) Von Neumann architecture

- (ii) Harvard architecture

- (iii) Super Harvard architecture

#### 1.4.1 Von Neumann Architecture

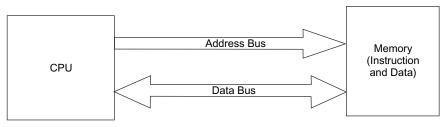

Figure 1.13 shows the Von Neumann architecture of processors and this architecture is most commonly used in processors. In this architecture, one memory chip is used to store both instructions and data. The processor interacts with the memory through address and data buses to fetch instructions as well as data.

Fig. 1.13 Von Neumann architecture of processors

#### 1.4.2 Harvard Architecture

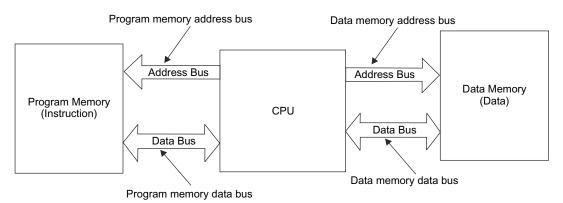

Figure 1.14 shows the Harvard architecture of a processor. In this processor architecture, two separate memory blocks, namely, program memory and data memory are used. The program memory is used to store only instructions and data memory is used to store data. The program memory address bus is used to locate the program memory and through program memory data bus, the processor can write/read instructions to/from memory. Similarly, the data memory address bus is used to locate data memory data bus can be used to access the data memory. Consequently, this architecture is efficient than Von Neumann architecture as the instructions and data will be accessed very fast.

Fig. 1.14 Harvard architecture of a processor

#### 1.4.3 Super Harvard Architecture

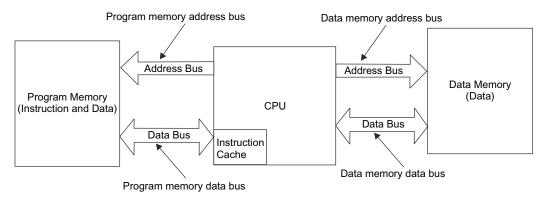

Figure 1.15 shows the super Harvard architecture which is the modified Harvard Architecture Generally, the data memory is accessed more frequently than the program memory in Harvard architecture. In the super Harvard architecture, the program memory can store secondary data to balance the load on both program memory and data memory. The instruction cache is in-built within the processor. This architecture is most commonly used in Digital Signal Processing (DSP).

#### 8 Microprocessors and Microcontrollers

Fig. 1.15 Super Harvard architecture

### **1.5** HISTORY OF MICROPROCESSORS

The history of computation began with the abacus. The abacus is a manual device. In an abacus, numerical information can be represented in physical form, and this information can also be manipulated in physical form to produce the necessary output. Even a thousand years before Christ, the abacus was very well-known and extensively used for arithmetical calculations. Consequently, it was known as the first actual machine which was used to perform addition, subtraction, division and multiplication.

In 1643, Blaise Pascal, a French mathematician and philosopher, invented the first mechanical calculator to perform addition as well as subtraction. In the 17<sup>th</sup> century, the multiplication and division facilities were added by the German mathematician Gottfried Leibniz.

In 1832, the Difference Engine was developed by Charles Babbage, a professor of mathematics at Cambridge University. This machine could add, subtract, multiply, divide and perform a sequence of steps automatically. In 1887, Herman Hollerith invented a device for automatic census tabulation. The first large-scale electronic digital computer was designed and constructed at the Moore school of Electrical Engineering of the University of Pennsylvania. In 1943, JW Mauchly and J Presper Eckert prepared a proposal for the US army to build an Electronic Numerical Integrator and Computer (ENIAC), and subsequently they started construction of the ENIAC. In 1944, the ENIAC team members began work on stored program computers Then ENIAC was finally ready in 1946. It occupied a room approximately of 12 m × 6 m. It contained nearly 18000 vacuum tubes and its power consumption was about150 kW. It operated on numbers with ten decimal digits. Addition could be carried out at the rate of 5000 calculations per second, multiplication at 350 per second and division at 166 per second. It was able to store upto 20 different numbers and recall them immediately whenever required. After that, John Von Neumann developed an improved version of ENIAC with the help of all ENIAC team members.

In 1949, the Electronic Delay Storage Automatic Calculator (EDSAC) was developed by Maurice Wilkes at University Mathematical Laboratory, Cambridge University. In 1951, the Universal Automatic Computer was built. In 1952, the Electronic Discrete Variable Automatic Computer (EDVAC) was developed by JW Mauchly and J Presper Eckert. This was the first electronic machine to use binary arithmetic. It operated on binary numbers of 43 digits and could store over 1000 numbers for immediate recall. This was also the first machine to use an external store using magnetic recording.

After World War II, scientists made great achievements in solid-state technology development and invented the transistor, i.e., a solidstate device, in 1948, at Bell Laboratories. Initially, germanium was the chief material for making the early semiconductor devices such as transistors. The use of silicon lowered

costs, because silicon is much more plentiful than germanium. The mass-production methods made transistors common and inexpensive. Then computer designers started to work on how to use transistors place of vacuum tubes in the late 1950s.

In the early 1960s, the American firm International Business Machines (IBM) manufactured huge solidstate scientific computers named IBM 7090 using solidstate technology. These systems required air-conditioned rooms. Usually, these systems were used for commercial and scientific applications to process large amounts of data. The cost of these computers was very high. So, the work on building small computers had been started. In the 1960s, the semiconductor industry developed a way to integrate a number of transistors on one silicon wafer. The transistors were connected together with small metal traces. When the transistors were connected together, they became a circuit which performed different functions such as gate, flip-flop, register, counter or adder. This new technology created the basic semiconductor building blocks. The building blocks or circuit modules made this way were known as an Integrated Circuit (IC). From then on, integrated circuits became feasible and the integration has been developed with time. There are three different stage of development of ICs from the period 1961 to 1972, namely, Small Scale Integration (SSI), Medium Scale Integration (MSI) and Large Scale Integration (LSI). In general, an SSI chip has dozens of transistors with their associated circuit components, but an MSI chip has hundreds of transistors and an LSI chip has thousands of transistors.

Due to development of SSI, MSI and LSI ICs, desktop computers were built at the end of the 1960s. These desktop computers were called *minicomputers* which were used in scientific applications. In the late 1960s and early 1970, Large Scale Integration (LSI) became common. Large-scale integration was making it possible to produce more and more digital circuits on a single IC. In 1965, Gordon More noted that the number of transistors on a chip doubled every 18 to 24 months. He made a prediction that semiconductor technology will double its effectiveness every 18 months. After that the next stage of development was started by the active research and development effort on solid-state technology. This stage of development was called Very Large Scale Integration (VLSI). By the 1980s, VLSI gave us ICs with over 100,000 transistors.

The microprocessor is an integrated circuit and it is the combination of solid-state technology development and the advancing computer technologies. It was developed in the early 1970s using LSI. It performs both control and processing functions having the low cost of a device and the flexibility of a computer.

### **1.6** EVOLUTION OF MICROPROCESSORS

In 1971, the Intel Corporation introduced the first 4-bit microprocessor 4004 which was developed using LSI technology. In 1972, the 8-bit microprocessor 8008 was produced by Intel. These microprocessors were not able to survive as general-purpose microprocessors due to their limitations and low performances. The first general-purpose 8-bit microprocessor 8080 was developed in 1974 by Intel. The microprocessor 8085 followed 8080 with some additional features. The limitations of 8-bit microprocessors were low operating speed, limited memory-addressing capability, less number of general-purpose registers and less number of instructions. To overcome all limitations of the 8085 microprocessor, computer scientists and designers worked to develop more powerful processors in terms of architecture, operating speed, memory and instruction set. As a result, a 16-bit microprocessor 8086 was developed in 1978.

Thereafter, the 80186 processor was designed with few more instructions and additional on-chip circuits such as clock generators, timers, DMA controllers and interrupt controllers, but the addressing capability was same as the 8086 microprocessor in 1982. But due to need of large memory in advance applications, processor designers put effort to design advanced microprocessors. The 80286 microprocessor is the first advanced microprocessor with proper memory management and protection abilities. It was developed by Intel in 1982 and it has an address capability of 16 Mbyte and its operating frequency is 12.5 HMz. The semiconductor technology could support the fabrication of a CPU with a 32-bit word size and higher operating frequency.

Hence, the 32-bit processor 80386 was developed. The first 32-bit processor was 80386. The numerical processor 80387 is compatible with 80386. In 1989, the 80486 was developed by Intel which combines all the features of 80386 after incorporating the math processor 80387 inside processor.

After the 80486 microprocessor, the Pentium family of processors was developed. The name Pentium was derived from the Greek *pente*, meaning 'five', and the Latin ending *-ium*. The term 'Pentium processor' refers to a family of microprocessors that share a common architecture and instruction set. The original Pentium processor was a 32-bit microprocessor produced by Intel. The first Pentium processors, P5, were developed in 1993. The P5 processor operated at a clock frequency of either 60 MHz or 66 MHz. This processor had 3.1 million transistors. The next version of the Pentium processor family, the P54C processor, was introduced in 1994.

In 1996, the Pentium MMX was introduced with the same basic micro-architecture with MMX instructions, and larger caches. The P55C (or 80503) Pentium MMX was introduced by Intel in October 1996 and it was based on the P5 core. It featured a new set of 57 MMX instructions intended to improve performance on multimedia tasks.

The Pentium Pro is a sixth-generation x86 microprocessor developed and introduced by Intel in November 1995. It was based on the P6 micro-architecture. While the Pentium and Pentium MMX had 3.1 and 4.5 million transistors, respectively, the Pentium Pro contained 5.5 million transistors.

The Pentium II processors refer to Intel's sixth-generation micro-architecture called 'Intel P6', introduced in May 1997. This processor consisted of 7.5 million transistors. The Pentium II was an improved version of the first P6-generation core of the Pentium Pro CPUs, which contained about 5.5 million transistors. In early 1999, the Pentium II was superseded by the Pentium III.

The Pentium III processors were based on the sixth-generation Intel P6 microarchitecture introduced in February 1999. These processors were very similar to the earlier Pentium II microprocessors with the addition of the SSE instruction set to accelerate floating point and parallel calculations. The first Pentium III variant was the *Katmai*, Intel 80525. It was first released at speeds of 450 and 500 MHz. Two more versions were released: 550 MHz in May 1999 and 600 MHz in August 1999. It was built on a 0.18 µm process. Pentium III Coppermines running at 500 to 733 MHz were first released in October 1999. From December 1999 to May 2000, Intel released Pentium IIIs running at speeds of 750, to 1000 MHz (1 GHz). The third revision, Tualatin (80530), was a trial for Intel's new 0.13 µm process. Pentium III Tualatins were introduced during 2001 and these processors could operate at speeds of 1.0 to 1.4 GHz. Tualatin performed quite well, especially in variations which had 512 KB L2 cache.

The Pentium III was eventually superseded by the Pentium 4. The Pentium 4 brand refers to Intel's line of single-core mainstream desktop and laptop central processing units developed in November 2000. This processor had the 7th-generation micro-architecture, called NetBurst. The original Pentium 4, codenamed 'Willamette', ran at 1.4 and 1.5 GHz and was released in November 2000 on the Socket 423 platform. In 2004, the initial 32-bit x86 instruction set of the Pentium 4 microprocessors was extended by the 64-bit x86-64 set. Pentium 4 CPUs introduced the SSE2 and, in later versions, SSE3 instruction sets were released to accelerate calculations, transactions, media processing, 3D graphics, and games. In 2005, the Pentium 4 was complemented by the Pentium D and Pentium Extreme Edition dual-core CPUs.

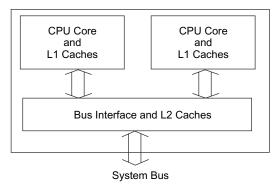

A dual-core processor is a CPU with two separate cores on the same die, each with its own cache. It is the equivalent of getting two microprocessors in one. The dual core processor is the first double core technology from Intel. It is a better performer than all previous processors in the Pentium series. A maximum of 2.33 GHz is available for model no. T2700 with a 2 MB L2 cache and a maximum of 667 MHz speed. The AMD Athlon 64 X2 Dual-Core Processor was developed in 2007. This processor can support SSE, SSE2, SSE3, MMX<sup>TM</sup>, 3D technology and legacy x86 instructions.

Intel Core 2 Extreme Quad-Core Processor QX6000 was introduced by Intel in 2007. This processor is designed to deliver performance across applications and usages in Internet, image processing, video content

creation, 3D, CAD, games, speech, multimedia and multitasking user environments. Intel 64 architecture enables the processor to execute operating systems and applications written to take advantage of the Intel 64 architecture. Quad-core processors are available in the FC-LGA6 package with a 2x4 MB L2 cache.

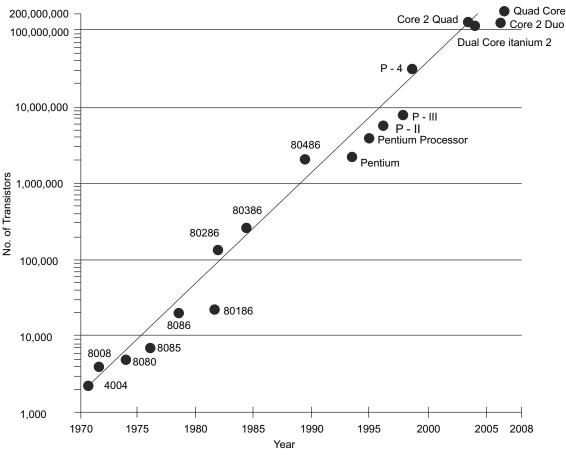

The Intel Core 2 Duo processor uses architecture to create two cores on a single die or in other words, there are two chips. It has better performance than dual-core processors in almost all benchmarking tests. They can be easily overclocked up to 4.0 GHz with suitable coolers. The Intel Core 2 Duo processor E8000 and E7000 series are 64-bit processors that maintain compatibility with IA-32 software and are based on the Enhanced Intel Core micro-architecture. These processors use Flip-Chip Land Grid Array (FC-LGA8) package technology, and plug into a 775-land surface mount, Land Grid Array (LGA) socket. These processors are based on 45 nm process technology. The Intel Core 2 Duo processor E8000 series features a 1333 MHz Front Side Bus (FSB) and 6 MB of L2 cache. The Intel Core™ 2 Duo processor E8300 and E7200 were released in April 2008. The Intel Core 2 Duo processor E7600 was developed in June 2009. These processors are used in Internet audio and streaming video, image processing, multimedia, and multitasking user environments. The differences between microprocessors are word length, size of the memory and speed at which the microprocessor can execute instructions. The comparison between different microprocessors is shown in Table 1.1. Figure 1.16 shows the evolution of processors with respect to the year of development and number of transistors in the processor.

| Microprocessor                     | No. of<br>Transistors      | Data bus/<br>Word | Address<br>bus | Memory<br>address          | Clock<br>frequency | Pin       | Year of<br>development |

|------------------------------------|----------------------------|-------------------|----------------|----------------------------|--------------------|-----------|------------------------|

|                                    | length                     |                   |                | range                      | Jiequency          | <br> <br> |                        |

| 4004                               | 2300                       | 4-bit             | 10-bit         | 640 B/1 KB                 | 75 kHz             | 16        | 1971                   |

| 8008                               | 3500                       | 8-bit             | 14-bit         | 16 KB                      | 0.5–.8 MHz         | 18        | 1972                   |

| 8080                               | 6000                       | 8-bit             | 16-bit         | 64 KB                      | 2 MHz              | 40        | 1974                   |

| 8085                               | 6500                       | 8-bit             | 16-bit         | 64 KB                      | 3–6 MHz            | 40        | 1976                   |

| 8088                               | 29 K                       | 8-bit/16-bit      | 20-bit         | 1 MB                       | 5-10 MHz           | 40        | 1980                   |

| 8086                               | 29 K                       | 16-bit            | 20-bit         | 1 MB                       | 5-10 MHz           | 40        | 1978                   |

| 80186                              | 29 K                       | 16-bit            | 20-bit         | 1 MB                       | 5-16 MHz           | 68        | 1982                   |

| 80286                              | 134 K                      | 16-bit            | 24-bit         | 16 MB real<br>4 GB virtual | 6–12.5 MHz         | 68        | 1982                   |

| 80386                              | 275 K                      | 32-bit            | 24/32-bit      | 4 GB real<br>64 TB virtual | 20 <b>-</b> 33 MHz | 132       | 1985                   |

| 80486                              | 3200 K                     | 32-bit            | 32-bit         | 4 GB real<br>64 TB virtual | 25-100 MHz         | 168       | 1989                   |

| Pentium                            | 3200 K                     | 32-bit            | 32-bit         | 4 GB real                  | 60–200 MHz         | 264       | 1993                   |

| Pentium Pro                        | 5500 K                     | 32-bit            | 36-bit         | 64 GB                      | 150-200 MHz        | 387       | 1995                   |

| Pentium II                         | 7500 K                     | 32-bit            | 36-bit         | 64 GB                      | 233-400 MHz        | 387       | 1997                   |

| Pentium III                        | 9500 K                     | 32-bit            | 36-bit         | 64 GB                      | 600–1000 MHz       | 387       | 1999                   |

| Pentium 4                          | 55000 K                    | 32-bit            | 36-bit         | 64 GB                      | 1.3–2 GHz          | 478       | 2001                   |

| Dual-Core<br>Processor<br>(Athlon) | 1.72 billion               | 64-bit            | 40-bit         | 1 TB                       | 2.93 GHz           |           | 2007                   |

| Core 2 Duo<br>processor E8500      | 410 million<br>transistors | 64-bit            | 40-bits        | 1 TB                       | 3.16 GHz           | 775       | 2008                   |

Table 1.1Comparative study of different microprocessors: 4004, 8085, 8086, 80186-80486, Pentium and<br/>Core 2 Duo

Fig. 1.16 Evolution of microprocessors

## **1.7** MICROPROCESSOR APPLICATIONS

The microprocessor started as a 4-bit device. It has progressed to an 8-bit, a 16-bit, a 32-bit and now a 64-bit device. A microprocessor with a longer word length will solve more problems at a faster rate. Therefore, a longer word length should give a better and faster solution to all problems. However, the consideration of product cost is important and it has been increased by number of data bits. The applications of 4-bit, 8-bit and other microprocessors are given below:

**Applications of 4-bit Microprocessors** The 4-bit microprocessors are very suitable for simple applications, namely, children's toys, calculators, microwave ovens, telephone diallers, etc. The 4-bit microprocessor based system cost is low. Generally, we will find the 4-bit microprocessor in

- + Toys: Robots, remote-controlled cars, handheld games

- + Calculators: Financial, scientific, database

- + Power Tool Controllers: Speed controls, sequencers, measurement devices

- + Computer Peripherals: Keyboard scanners, simple printers, clocks

- Other Simple Applications: Microwave ovens, telephone diallers, smart thermostats, shortwave scanners, TV remote controls

**Applications of 8-bit Microprocessors** The 8-bit microprocessor-based system is more costly than a 4-bit microprocessor-based system. It is used where memory requirement is large and fast operation is also required. The examples of 8-bit microprocessor applications are given below:

- **• Toys:** Video games, programmable robots

- Complex Intelligent Product Controllers: VCR control and programming, security systems, and lighting system controllers

- + Computer Peripherals: Video display, higher-speed printers, modems, plotters, and communication controllers

- + Industrial Controllers: Robotics, processing control, sequence control and machine tool control

- + Instruments: Logic analyzers, communication analyzers, disk-drive testers, digital oscilloscopes, and smart voltmeters

**Applications of 16-bit, 32-bit and 64-bit Microprocessors** The 16-bit, 32-bit and 64-bit microprocessors are used in graphic oriented CAD and CAM systems. The 32-bit and 64-bit microprocessors feature very fast operation, extreme computing power, and megabytes, or even gigabytes, of main memory-addressing space. The list of applications where microprocessors have been already used are illustrated below:

- + Communications: Data, voice, mobile, electronic switching, routing

- + Intelligent Instruments: CRT terminals, digital multimeters, synthesizers, oscilloscopes and counters. Microcontrollers are used in military equipment, radars, tanks, etc.

- + Automatic Test Equipment: Automatic test equipment at all levels from development, fabrication, component testing assembly, PCB, module and system testing

- + Electrical Power System: Data acquisition, logging, protection, metering, control and processing, automatic control of generators, voltage and fuel control of furnaces in a power plant

- Industrial Process Control: Instrumentation, monitoring and control, data acquisition, logging and processing

- + Traffic Control: Traffic light control for road crossing

- + Electronic Games: Various games possible, quizzes and self-teaching

- + Household Appliances: Cooking ovens, washing machines and other appliances have started using microprocessors since they replace much electronic hardware at lower cost

- + Medical Electronics: Quick patient check-up, diagnosis, blood analysis, ECG, etc.

- Database Management: Computers are used for word processing, database management, storing information, to connect any institution/organisation to other institutions/organisations through Internet

## **1.8** EVOLUTION OF MICROCONTROLLERS

A microcontroller is a small computer on a single Integrated Circuit (IC) containing a processor, memory, and programmable input/output ports. The program memory, in the form of flash or ROM, is also incorporated on

a chip and a small amount of RAM is also included on a single chip. Microcontrollers are specially designed for embedded applications.

After the innovation of 8080 microprocessors in 1975, Intel Corporation started research on developing an IC which could be used as a microprocessor and should have on-chip data storage. Consequently, Intel developed the first dedicated microcontroller (MCU) chip 8048 IC in 1976. The 8048 IC, was known as MCS-48 microcontroller and it had only 1-byte instructions.

In 1980, Intel had developed an 8-bit microcontroller named the 8051 microcontroller. It had 128 bytes of RAM, 4 K bytes of on-chip ROM, two timers, four parallel ports with each port 8-bits wide and a serial port. This microcontroller had 2-byte instructions. Thereafter, the 8052 microcontroller was developed. This microcontroller had all the standard features of 8051 with an extra 128 bytes of RAM, 4K bytes of ROM and an extra timer. Therefore 8052 had 256 bytes of RAM, 8 K bytes of ROM and three timers. The 8031 microcontroller is also a member of the 8051 family. This microcontroller has all features of 8051 microcontroller except 0 K bytes on-chip ROM. Table 1.2 shows the salient features of 8051, 8052, 8031 and 8032 microcontrollers.

| Microcontroller<br>IC | ROM<br>(on-chip<br>program<br>memory) | RAM<br>(on chip<br>data<br>memory) | No.<br>of<br>timers | No.<br>of pins<br>in DIP | No.<br>of I/O<br>pins | No. of<br>vector<br>interrupts | Full<br>duplex<br>serial I/O<br>port |

|-----------------------|---------------------------------------|------------------------------------|---------------------|--------------------------|-----------------------|--------------------------------|--------------------------------------|

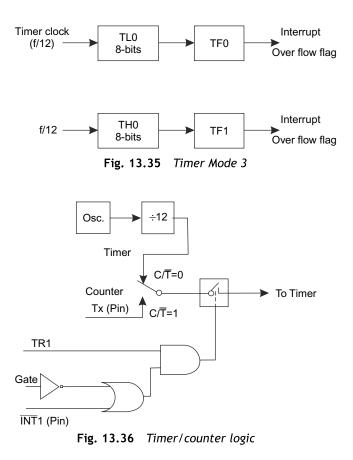

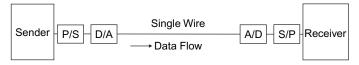

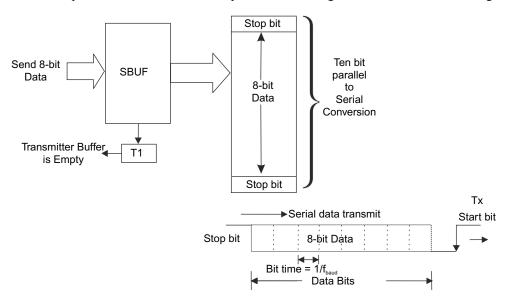

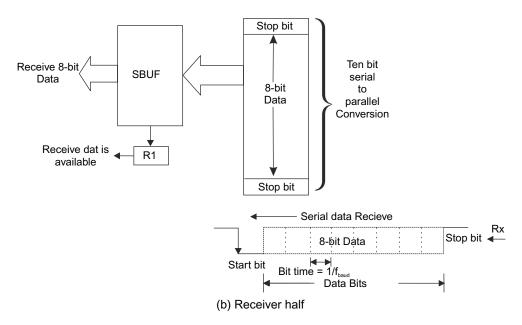

| 8051                  | 4K bytes                              | 128 bytes                          | 2                   | 40                       | 32                    | 5                              | 1                                    |